中頻軟件無線電系統的FPGA實現方案

一、 引言

本文引用地址:http://www.j9360.com/article/190707.htm現代通信技術、微電子技術和計算機技術的飛速發展,促進了無線通信技術從數字化走向軟件化。軟件無線電的出現掀起了無線通信技術的又一次革命,它已經成為目前通信領域中最為重要的研究方向之一。所謂軟件無線電,是指構造一個通用的、可重復編程的硬件平臺,使其工作頻段、調制解調方式、業務種類、數據速率與格式、控制協議等都可以進行重構和控制,選用不同的軟件模塊就可以實現不同類型和功能的無線電臺,其核心思想是在盡可能靠近天線的地方使用寬帶A/D和D/A變換器,并盡可能地用軟件來定義無線功能[1]。

軟件無線電具有極大的應用價值和廣泛的應用前景。在軍事上,不但可以解決不同無線設備間的互連互通,而且還可以現場開發新波形。在商業方面,可實現移動通信的無縫接入和完全自由的個人通信,縮短系統的開發周期和降低運營商的成本,現已成為3G和4G所采用的一項關鍵技術。

本文研究了中頻軟件無線電的實現方案,并設計了基于FPGA的通用硬件平臺。在此平臺上,通過PC機下載軟件,實時實現了軟件無線電中頻至基帶的波形處理和多種不同的調制解調方式。

二、 軟件無線電的系統結構

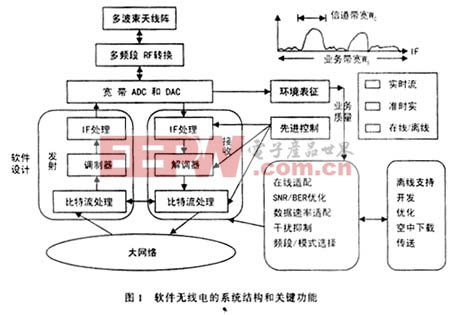

軟件無線電賦予了無線電臺多種特性。如圖1所示,軟件無線電用軟件定義了包括RF信道接入和波形合成等空中接口的所有方面,寬帶ADC和DAC在中頻轉換每個RF業務頻段成為模擬和數字形式,帶寬為WS的寬帶數字接收機信號流包括了全部用戶信道,其中每個用戶的帶寬Wc《WS 。

在圖1所示的軟件無線電中,中頻ADC和DAC信道可以同時使用可編程的數字硬件和軟件來處理。中頻處理包括:用來分離用戶信道的濾波;數字波束成形;空時聯合均衡;空間分集、極化或頻率分集信道的綜合,以及捕獲高質量波形的其它方法。一般情況下,需要多個中頻,或者用零中頻來處理。數字下變頻技術可以利用帶通波形抽樣信號的頻域周期性,將帶通波形直接變換到基帶。

在軟件無線電的發射機中,基帶信號由軟件實現的信道調制解調器轉換成抽樣后的信道波形,驅動高性能DAC。中頻處理軟件還可以對基帶信號進行預加重或非線性預編碼處理。具體實現時,調制解調功能、中頻處理和RF信道接入可以合并成一個部分,例如直接轉換接收機。另外,軟件或各種特性間實時轉換的動態編譯允許這些分立的功能集成到一個如FPGA這樣的器件中。

三、 中頻軟件無線電實現方案的研究

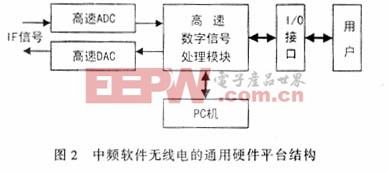

典型的中頻軟件無線電的通用硬件平臺結構如圖2所示,包括A/D變換器、D/A變換器、數字信號處理模塊和PC機,具有很強的靈活性和高度的開放性。

圖2中的數字信號處理模塊用來實現多媒體處理、調制解調、波形處理、上/下變頻和控制等功能。此模塊可以靈活擴展,滿足不同無線通信系統對數字信號處理的運算速度和運算量的要求。PC機具有良好的人機接口,可以完成如下功能:初始化系統;提供軟件開發環境;實現在線/離線開發應用軟件;下載軟件到數字信號處理模塊等等。

1. 軟件無線電中數字信號處理能力所面臨的挑戰

數字信號處理模塊是軟件無線電的核心部分。軟件無線電要求數字信號處理模塊能實時處理ADC變換后的數字信號,并用軟件的方法來實現大量的無線電功能,這些功能包括:編解碼、調制解調、濾波、同步、盲均衡、檢測、數據加密、傳輸加密糾錯、跳擴頻及解擴和解跳、通信環境評估、信道選擇等,而單個DSP根本無法完成這些功能,對于基站則差距更大。 考慮單個信道的情況,最基本的解調需要10次操作/秒,一個性能良好的FIR/IIR信道選擇濾波器需要100次操作/秒,再加上均衡、解交織、信道解碼、解復用、差錯控制等等。對于一個采樣率為30~50MHz的信道,所需要的處理速度很容易就達到了5000MIPS(每秒百萬指令)。文獻[2]對單信道DSSS(直接序列擴頻)軍事波形的處理需求進行了估計:此波形的碼片速率為10 Mchip/s,ADC的采樣率為40 MSPS,數據速率為9 600 bit/s,完成脈沖成形、PN(偽隨機)碼產生、解復用、解擴/相關、載波同步、跟蹤、Viterbi譯碼、盲均衡和控制等功能;全部所需要的處理速度大約為12.78 GFLOPS(每秒十億次浮點操作)。現在3G所使用的寬帶CDMA技術,單信道所需要的處理速度的量級也與上述軍事波形相當,甚至更高。對于基站,由于需要處理很多信道,所需要的處理速度會達到上千GIPS(每秒十億指令)的量級。

然而目前可用的一些高速DSP的性能,最快的也不超過5 GIPS,與實際需求相差巨大。這種處理資源的匱乏,被稱之為DSP瓶頸[3],是影響軟件無線電發展的一個至關重要的技術挑戰。

2. 實現中頻軟件無線電系統的傳統方法

為解決數字信號處理資源匱乏這一問題,目前實現中頻軟件無線電系統的傳統方法有2種,即用多個DSP實現和用DSP+參數化ASIC實現。

(1)多個DSP方法

這種方法一般采用多個DSP組成樹狀或網狀結構,并行處理數據流,但這種方法最大的弊端是系統體積大、供耗高、成本高。

(2)DSP+參數化ASIC方法

這種系統是目前較多采用的實現方法。在這種系統中,參數化ASIC可有限編程,完成對數字信號處理速度要求較高的部分,DSP做較低速的數字信號處理。這種方法雖然減小了系統的體積,降低了功耗,但是由于參數化ASIC可編程的限制較大,嚴重地限制了系統的靈活性和開放性,難以體現軟件無線電的優越性。

3.用FPGA實現中頻軟件無線電的優勢

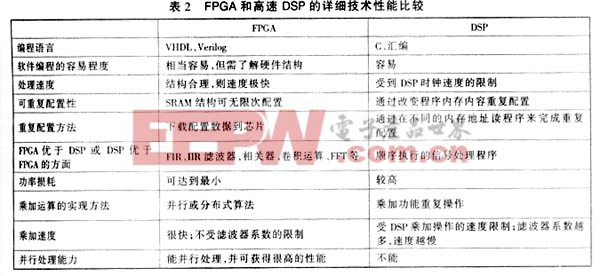

本文采用FPGA來實現中頻軟件無線電。表1和表2所示的比較分析表明,FPGA與參數化ASIC、DSP比較有很多優勢,它不但在功耗、體積、成本方面優于參數化ASIC、DSP,而且處理效率高、現場可編程性能良好。不同于DSP的單流處理方式,FPGA是多流并行處理,這種處理方式使FPGA能完成DSP難以實現的許多功能,如FIR/IIR濾波器、擴頻、跳頻模式。因此,FPGA能很好地體現軟件無線電的靈活性和開放性,很適合在軟件無線電中做高速數字信號處理,是實現中頻軟件無線電的理想選擇。

4.采用FPGA實現中頻軟件無線電系統

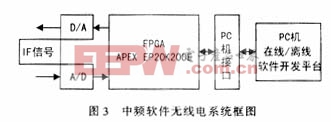

圖3為所實現的中頻軟件無線電系統框圖。系統從IF(中頻)進行A/D和D/A變換。下面就系統的各部分做一介紹。

1 寬帶D/A和A/D轉換器

D/A和A/D轉換器分別把中頻數字信號轉換成模擬信號,中頻模擬信號轉換成數字信號。D/A變換器和A/D變換器的選擇,直接關系到軟件無線電的總體性能。因此,必須根據系統的要求,綜合考慮D/A變換器和A/D變換器的各方面性能,做出選擇。

(1)寬帶D/A轉換器

選用了AD公司的AD9713B,性能指標如下:

1)具有12 bit精度;

2)轉換速率最快為80 MSPS;

3)SFDR(無雜散動態范圍)為70 dBc。

這里,DAC鎖存時鐘為40 MHz。AD9713B后接兩級放大器,將模擬信號放大后輸出。

(2)寬帶A/D轉換器

在軟件無線電中,對ADC的性能要求很高,ADC的選擇比DAC更為重要。選擇ADC時,需要考慮其采樣頻率、帶寬、轉換位數和SFDR。而這幾個性能指標是互為約束的,必須綜合考慮確定。

在此,ADC選用AD公司生產的AD9042。AD9042是高速、高性能、低功耗的單片12位模/數變換器,其性能指標如下:

1)最大采樣速率41 MSPS;

2)SFDR為80 dBc;

3)信噪比為68 dB。

實際使用中,采樣時鐘為40 MHz,AD9042的性能很好。

2FPGA——數字信號處理模塊

FPGA選用了Altera公司的APEX EP20K200E器件,這個器件為20萬門容量,1.8 V低功耗,具有多種I/O接口和多鐘配置方式的單片系統級集成的可編程邏輯器件。

FPGA主要完成數字上/下變頻、濾波、調制/解調、擴頻/解擴、載波以及PN(偽隨機碼)的同步和跟蹤等功能。

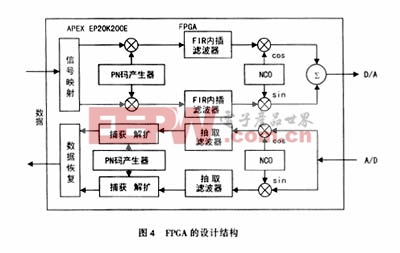

FPGA的設計結構如圖4所示。在此,以DSSS(直接序列擴頻)信號為例說明。發射的設計為,系統將125 kbit/s的數據映射成上下支路各62.5 kbit/s的數據與PN碼產生器輸出的4Mchip/s的PN碼相乘擴頻,然后由14 bit 的FIR濾波器完成內插濾波,濾波器輸出的信號為20 MHz,與NCO相乘上變頻至中頻,并取高12 bit輸出至D/A變換器。接收的設計與發射相對應,A/D變換器輸出的40 MHz的12 bit中頻數字信號與NCO相乘正交下變頻成I、Q兩路信號,這2路信號經抽取濾波變為20 MHz的基帶信號,輸入到解擴電路完成PN碼的捕獲、解擴(用[HJ71mm]てヅ瀆瞬ㄆ饗喙仄魘迪鄭┮約靶藕畔喙睪蟮墓β始觳猓解擴后的信號和檢測到的功率信號輸入到碼跟蹤電路完成碼元跟蹤,最后完成解碼,恢復數據。完成這些功能,所占的FPGA資源為:7142個LE(邏輯單元),16896 ESB(嵌入式邏輯塊) bits。

3 PC機及其接口

PC機為FPGA提供軟件開發環境,完成在線/離線的軟件開發和調試,并通過RS232口與FPGA通信,實時下載軟件到FPGA。

五、 系 統 性 能

系統采用FPGA完全實現了中頻軟件無線電系統的軟件可編程,具有很高的靈活性、開放性和通用性。設計的FPGA軟件模塊,如NCO、數字濾波器等可為多種調制/解調模式所使用。各種調制/解調模式相應的配置軟件以文件的形式存儲在微機里,可根據具體要求下載到FPGA,從而實現調制/解調模式的實時改變。經測試,系統采用的時鐘為40 MHz時,可達到的工作性能如下: (1)中頻載波:可以任意設置,最高可達16 MHz,最大頻率誤差為0.009 Hz;

(2)信息速率:可變,最高可達4 Mbit/s;

(3)調制/解調模式:通過更換軟件,系統可實現AM、PM、FM、BPSK、QPSK、DSSS等模式。

六、 結論

FPGA在軟件無線電中的應用已經越來越被人們所重視。用FPGA來實現中頻軟件無線電系統具有很高的靈活性和開放性,充分體現了軟件無線電的優越性,是當前實現軟件無線電技術的理想方案。

評論