基于FPGA的循環冗余校驗實驗系統的實現

摘要:文章首先分析了循環冗余校驗碼的功能,在此基礎上提出了基于FPGA的實現方法,詳細闡述了CRC校驗編解碼的實現方法,并提出了基于現有的實驗箱設備實現小型的CRC校驗系統的總體設計框架和設計思路,完成了CRC校驗實驗系統的設計,充分提高了設備的使用效率。

關鍵字:循環冗余校驗 CRC編解碼 實驗系統

一、引言

隨著人們對數據業務的需求越來越多,數據通信在近來得到了長足的發展。但是由于通信信道傳輸特性的不理想和加性噪聲的影響,設備之間的數據通信常會發生一些無法預測的錯誤,為確保高效而無差錯的傳輸數據,降低錯誤而帶來的影響,必須對數據進行差錯檢測及控制。在諸多檢錯手段中,循環冗余檢測方法(CRC)是非常有效的一種方法。CRC是對傳送數據進行校驗的特點是:檢錯能力極強,開銷小,易于編程。從其檢錯能力來看,它所不能發現錯誤的幾率達0.0047%以下,從其性能及開銷上均遠遠優于奇偶校驗以及算術和檢錯等方式。因而,在數據存儲和數據通信領域,CRC無處不在。

FPGA是在PAL、GAL、PLD等可編程器件的基礎上進一步發展的產物,采用了邏輯單元陣列這樣一個新概念,內部包括可配置邏輯模塊CLB、輸出輸入模塊IOB和內部連線三個部分。用戶可對FPGA內部的邏輯模塊和I/O模塊重新配置,以實現用戶的邏輯。它還具有靜態可重復編程和動態在系統重構的特性,使得硬件的功能可以像軟件一樣通過編程來修改。FPGA如同一張白紙或是一堆積木,工程師可以通過傳統的原理圖輸入法,或是硬件描述語言自的設計一個數字系統。通過軟件仿真,我們可以事先驗證設計的正確性。因此,FPGA的使用非常靈活。利用FPGA實現CRC校驗是一個高效的切實可行的方法。

在教學過程中,我們嘗試利用現有的EDA實驗箱設備,設計實現小型的CRC校驗系統,拓展設備的功能,提高設備使用效率。

二、系統總體設計

循環冗余校驗CRC是數據通信領域中最常用的一種差錯校驗碼,其特征是信息字段和校驗字段的長度可以任意選定。它的基本原理是:在K位信息碼后再拼接R位的校驗碼,整個編碼長度為N位,因此,這種編碼又叫(N,K)碼。對于一個給定的(N,K)碼,可以證明存在一個最高次冪為N-K=R的多項式G(x)。根據G(x)可以生成K位信息的校驗碼,而G(x)叫做這個CRC碼的生成多項式。

校驗碼的具體生成過程為:假設發送信息用信息多項式C(x)表示,將C(x)左移R位,則可表示成C(x)*2R,這樣C(x)的右邊就會空出R位,這就是校驗碼的位置。通過C(x)*2R除以生成多項式G(x)得到的余數就是校驗碼。

生成多項式是接受方和發送方的一個約定,也就是一個二進制數,在整個傳輸過程中,這個數始終保持不變。在發送方,利用生成多項式對信息多項式做模2除(異或運算)生成校驗碼。在接受方利用生成多項式對收到的編碼多項式做模2除(異或運算)檢測,當被傳送信息(CRC

碼)任何一位發生錯誤時,被生成多項式做模2除(異或運算)后應該使余數不為0。

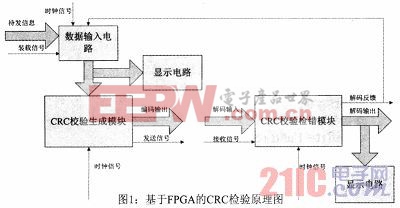

基于這樣的原理,利用FPGA實現的小型的循環冗余校驗實驗系統可以由五個部分組成:數據輸入電路、CRC編碼處理電路、CRC解碼處理電路、時鐘電路、顯示電路。作為CRC校驗的輸入部分,本設計采用通用的數字機械式鍵盤。本系統顯示信息電路采用共陰極8位7段數碼管顯示碼值,使用3-8譯碼器譯碼。CRC校驗結果提示電路用LED燈顯示,方便、簡潔。時鐘電路使用可調數字信號源產生時鐘。編解碼處理電路使用FPGA適配器。發送端首先將數據寫入設計好的FIFO存儲器,然后依次地調出數據進行編碼,然后將生成的CRC碼發送出去,并給以接收端一個接收信號;接收端收到信號后,開始對接收到的數據進行解碼,并將解碼信息反饋給發送方。當解碼正確時,發送方繼續發送下一個數據,當解碼錯誤時,發送方把剛發的數據重新調出,進行編碼,發送出去。系統原理圖見圖1。

fpga相關文章:fpga是什么

評論