YUV分離的兩種FPGA實現

摘要:速度與面積的互換一直是基于FPGA設計中的一個不變的主題,在此介紹了兩種YUV分離的FPGA的實現方式:基于面積的實現和基于速度的實現。前者僅用一片雙口RAM串行,實現了YUV分離數據的輸出;后者利用流水線的思想,基于兩片雙口RAM之間的乒乓操作,完成了模塊的設計。通過Verilog HDL對兩種方法進行了實現,并利用ModelSim完成了模塊仿真。通過對比發現,二者各有優勢:前者消耗硬件資源與面積較后者有很大改進;后者對提高整體系統實時性具有重大意義。因此,兩種實現方式從兩個角度為YUV的分離存儲提供了可行的解決方案。

關鍵詞:FPGA;YUV分離;雙口RAM;流水線

0 引言

隨著視頻采集、壓縮技術以及無線傳輸技術的飛速發展,基于FPGA的設計被廣泛應用到各個領域,尤其在嵌入式系統。傳統的視頻技術解決方案(如采用CPLD+CPU的結構進行的設計)已經不能滿足人們對于集成度與實時性的要求,而FPGA恰逢其時的出現,以其高度集成,并行處理和豐富的片上資源,同時隨著FPGA自身性能的不斷提高,各個FPGA廠商為視頻處理提供了越來越多的高性能解決方案,使得FPGA在視頻采集壓縮以及無線傳輸領域的應用越來越廣泛。

本文的研究是基于FPGA的實時視頻無線傳輸系統的一部分。在進入視頻壓縮編碼器之前,需要完成視頻的采集,模/數轉換,預處理,讀/寫SDRAM等操作,本文針對預處理過程中數字視頻的分離存儲進行了研究.即YUV的分離存儲,并采用了兩種方法實現了YUV的分離存儲;一種是基于面積考慮的只用一片雙端口存儲器的實現;另外一種是基于速度考慮的用兩片雙端口處理器的實現。

1 基于FPGA的實時視頻無線傳輸系統

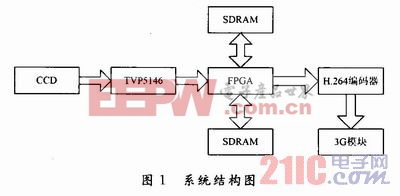

本文的系統主要由視頻采集、視頻壓縮、無線傳輸3大部分組成。系統結構如圖1所示。在視頻數據進入視頻壓縮編碼器之前,視頻需要經過CCD視頻采集、TVP5146視頻解碼、有效數據抽取、預處理、SDRAM存儲等操作。這些操作均屬于視頻采集前端系統。其中,CCD完成模擬視頻的采集,TVP5146完成對輸入模擬視頻到數字視頻的轉換,而這里需要對TVP5146進行內部寄存器設置,設置通過I2C總線來完成。有效

數據抽取模塊完成對有效視頻數據的抽取,1幀視頻數據由625行分屬于奇偶場的視頻組成,而系統所需要的是1幀視頻的576行有效數據中的特定像素,而這個工作就是由有效視頻抽取模塊完成;預處理模塊則是完成數字視頻的串/并轉換,即8位到16位的轉換以及YUV的分離,這也是本文所做的工作,下面將做詳細介紹;然后將視頻存儲在SDRAM中,實現了為H.264編碼器提供穩定的視頻流供壓縮;3G模塊將壓縮模塊

送出的視頻流進行RTP封裝,然后發送到遠端接收系統。

本文所做的研究是基于YUV分離開展的,前面已經提過面積與速度是FPGA設計不變的主題。二者也是一對矛盾體,不可能同時兼顧,在系統設計中只能通過速度和面積的互換來使二者有機的統一起來。其中,基于面積的設計是利用一片雙端口RAM,利用FPGA與SDRAM之間的頻率差異來實現的,選定的FPGA的工作頻率為48 MHz,SDRAM的工作頻率為100 MHz,這樣就實現了再一行視頻數據的有效期完成對雙端口RAM的寫,然后利用一行視頻數據的行消隱期,完成對雙口RAM的讀出操作,進而實現了YUV分離輸出;而另一種實現是基于速度的實現,利用兩片雙端口RAM進行乒乓操作,完成了數據的無縫緩存和處理。本文通過Verilog實現了兩種方法設計。通過對比仿真結果,均達到了預期結果。

電子鎮流器相關文章:電子鎮流器工作原理

評論