PCI仲裁器邏輯擴展設計方案解析

PCI總線是現(xiàn)今最為流行的控制總線之一,它廣泛地應用在計算機中,目前嵌入式設備中的很多解決方案都包含了PCI總線。在多主設備的PCI系統(tǒng)應用中,必須為各個主設備提供仲裁授權信號。為了使PCI設備能夠更方便地應用在嵌入式系統(tǒng)中,本文介紹一種基于飛思卡爾MPC5200B的低成本PCI總線仲裁器邏輯擴展的設計方法,此方法可以在已有的PCI仲裁器的基礎上,實現(xiàn)擴展PCI總線上主設備的個數(shù),從而滿足多PCI設備的設計要求,提高系統(tǒng)的擴展性要求,在體積、功能、成本等諸多方面都有很好的應用前景。

本文引用地址:http://www.j9360.com/article/190430.htmMPC5200B

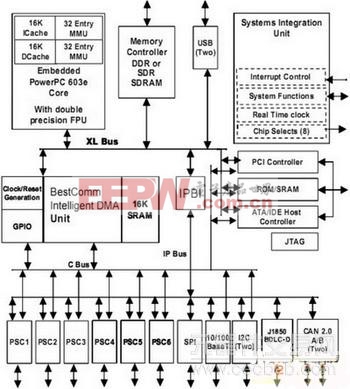

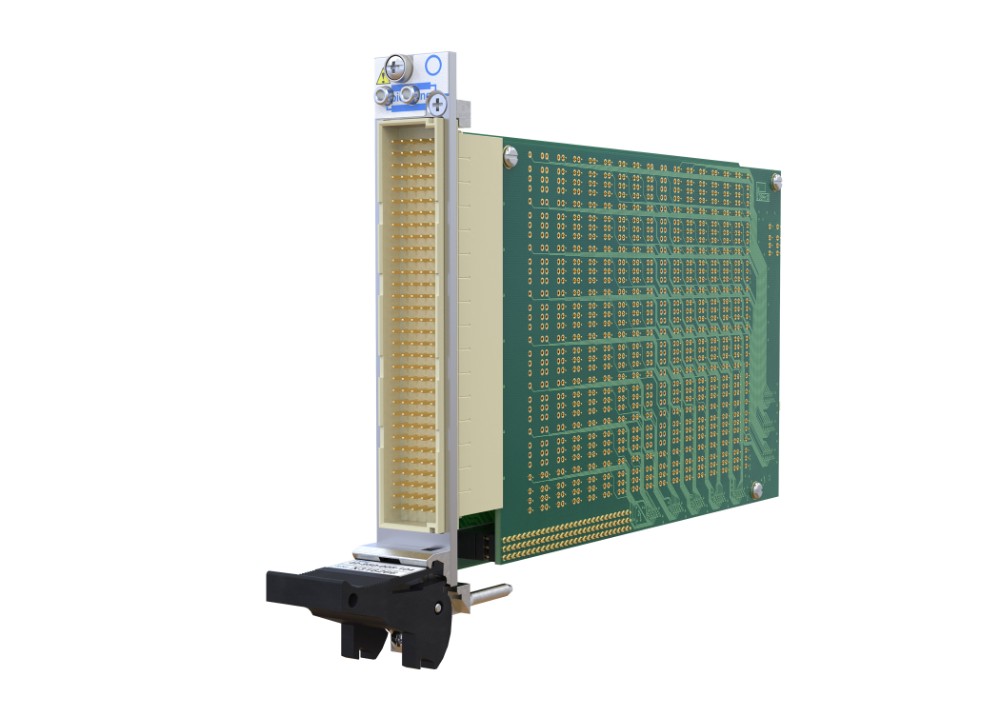

飛思卡爾公司的MPC5200B是基于PowerPC架構下的一款性能卓越的微處理器。它具有760MIPS、帶浮點運算單元(FPU)、低功耗等特點。該處理器采用高性能的e300內核,集成了高性能存儲控制器、中斷控制器、 DMA控制器、PCI控制器、以太網控制器以及USB、CAN 2.0A/B、I2C等豐富的接口。其結構框圖如圖1所示。

圖1 MPC5200B 框圖

MPC5200B能夠快速提供數(shù)據(jù)吞吐和處理。集成的 BestComm DMA控制器可降低主e300核心傳送I/O密集數(shù)據(jù)的負荷。集成的雙倍數(shù)據(jù)速率(DDR)內存控制器的有效內存總線速度達到266MHz,能夠實現(xiàn)高速數(shù)據(jù)訪問。 BestComm DMA 控制器和DDR內存支持的高速PCI 接口能夠實現(xiàn)高速數(shù)據(jù)輸入和輸出。

MPC5200B內部集成了一個PCI總線仲裁器,但其仲裁只支持兩個外部PCI主設備(包含MPC5200B的PCI模塊)。為了增加PCI主設備,我們必須對PCI仲裁器進行擴展。

PCI總線仲裁

PCI總線是一種共享式的總線,可以連接多個主設備,但由于數(shù)據(jù)傳輸?shù)莫毾硇裕恳粫r刻只能由一個主設備占用總線。因此,為了有效地利用PCI總線帶寬,總線上必須設置一個仲裁器。

每個具有主設備功能的PCI設備必須提供兩個與仲裁有關的信號:REQ#(請求總線信號)和GNT#(總線授權信號)。由需要發(fā)起PCI傳輸事務的設備發(fā)出 REQ#信號,由PCI總線仲裁器裁決后給出GNT#信號。接到GNT#信號的PCI設備將在下一次總線空閑后開始操作。

PCI總線仲裁的裁決過程可以在PCI傳輸期間完成,并不占用PCI總線的帶寬,這被稱為隱式仲裁:即需要發(fā)起PCI操作的設備可以隨時發(fā)出請求REO#,PCI仲裁器立即批準該請求并給出GNT#。但實際的傳輸過程一定要等到當前傳輸完畢、線空閑后才可以開始。

具體設計及仿真

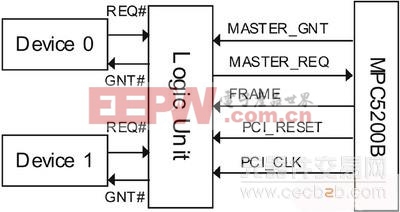

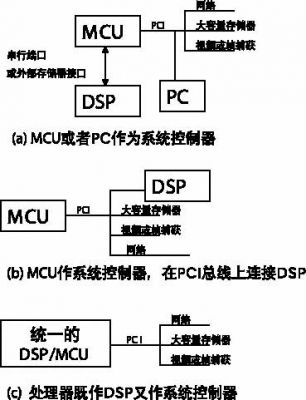

以MPC5200B外擴兩個主PCI設備為例,依據(jù)PCI仲裁原理及MPC5200B PCI控制器接口,邏輯擴展方式如圖2所示。其中邏輯單元(Logic Unit)就是本文詳細闡述的部分。

MPC5200B含有一個片上PCI總線仲裁器,現(xiàn)在需要對外擴展其仲裁功能,以滿足多主PCI設備的需求。

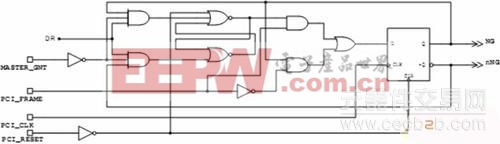

對于外擴PCI主設備而言,有兩對REQ#和GNT#信號需要和MPC5200B片上PCI仲裁器進行通訊;對于MPC5200B而言,邏輯單元就是它一對一的主PCI設備,通訊信號為相關的PCI總線控制信號。邏輯單元電路如圖3所示。

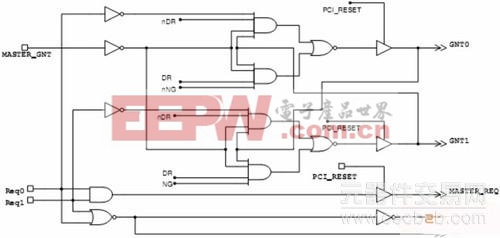

圖3 MPC5200B PCI仲裁邏輯擴展電路

圖3b MPC5200B PCI仲裁邏輯擴展電路(續(xù))

評論