基于FPGA的實時數字化光纖傳輸系統

摘要 提出一種實時數字化光纖傳輸系統,該系統分為發送端和接收端。發送端用A/D轉換器將輸入的模擬信號數字化,再用FPGA對數據進行處理,并通過光纖傳輸。同時,FPGA還控制A/D轉換器的工作。接收端用串行收發器TLK1501對接收數據進行解碼處理,還原有效信號。實驗表明,該系統實時性好、信號傳輸誤碼率低、工作性能穩定、抗干擾性強,系統具有可行性和有效性。

關鍵詞 光纖傳輸;FPGA;A/D轉換器;TLK1501;實時性

在電子設計領域中,通常要對多路寬帶信號進行實時采集、處理和傳輸。傳統的信號采集傳輸系統,采用專用集成電路控制A/D轉換器等外圍電路。由于專用集成電路時鐘頻率低、靈活性差、實時性低、傳輸速度慢、通用性差等缺點,難以滿足對高速寬帶信號采集和處理的要求。FPGA具有時鐘頻率高、速度快、采集實時性高、控制靈活等特點,與A/D轉換器等外圍電路結合,更適于高速數字信號處理。光纖傳輸與電氣傳輸相比,具有傳輸頻帶寬、通信容量大、傳輸損耗低、抗電磁干擾性能強、抗輻射能力強、保密性好、重量輕等特點,在通信領域被廣泛應用。

文中提出基于FPGA和光纖傳輸的高速數字信號傳輸方案。以帶有收發器的高性能FPGA為控制核心,控制外圍A/D轉換器和數據處理,通過光纖媒介進行數據傳輸,滿足高速數字信號實時處理和傳輸的

要求。

1 系統總體設計方案

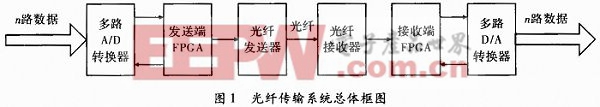

光纖傳輸系統是以光波為信息載體、光纖為傳輸媒介,用光來傳輸信息的傳輸系統。光纖傳輸系統總體框圖如圖1所示,發送端主要由A/D采集、FPGA數據預處理、光纖發送模塊組成;接收端主要由光纖接收模塊、FPGA數據后處理、D/A轉換模塊組成。兩者通過光纖進行通訊。

在發送端,先將外部輸入的模擬信號進行預處理,再通過A/D轉換器轉化為數字信號送入FPGA進行處理。根據數據傳輸以及通信協議的要求,FPGA將預處理后的A/D數據進行編碼、成幀。然后由FPGA內部的IP核進行并串轉換,最后由光收發模塊完成電光轉換后,通過光纖發送出去。

在接收端,光收發器模塊將接收到的光信號轉化為電信號,完成高速串行數據到并行數據的轉換;然后,將轉換后的并行數據送入FPG A,FPGA完成信號的解幀、解碼,并進行后處理,該過程是發送端的逆過程。最后,經D/A轉換器將接收到的數據恢復成模擬信號。

2 硬件電路設計

2.1 發送端硬件電路設計

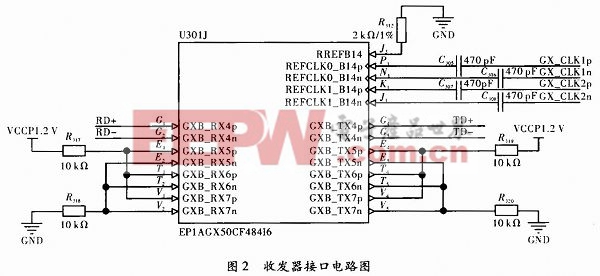

可編程邏輯器件FPGA是主控芯片,是系統的核心,設計選用Altera公司帶有收發器的Arria GX系列芯片EP1AGX50CF48416。芯片內部集成了4個收發器通道,傳輸數據率從600 Mbit·s-1到3.152Gbit·s-1,收發器每通道在2.5 Gbit·s-1時消耗功率僅為125 mW;收發器可利用固定均衡設置來均衡串行通道,實現發送預加重和接收均衡;收發器支持串行環回、反向串行環回以及偽隨機二進制序列(PRBS)產生器和校驗器。專用收發器接口電路如圖2所示。RREFB14接一個2kΩ/1%的參考電阻,其他未使用的收發管腳通過10kΩ電阻到電源或地。

光收發模塊選用MXP-243S-X型光收發器,其可處理的數據率為1.25 Gbit·s-1,單電源3.3 V供電,差分LVPECL電平輸入和輸出,發射和接收部分相互獨立。發射部分差分輸入阻抗100 Ω,傳輸光信號波長1310nm。光發射器電路圖如圖3所示。發射的差分數據接到FPGA的專用收發器的發射管腳G4和G5上,控制引腳直接接到普通L/O管腳,并通過上拉電阻接到電源。

評論