基于FPGA的高速實時數據采集系統設計

摘要:設計的基于FPGA的高速實時數據采集系統,可控制6路模擬信號的采集和處理,FPGA中的6個FIFO對數據進行緩存,數據總線傳給DSP進行實時處理和上傳給上位機顯示。程序部分是用Verilog HDL語言,并利用QuartusⅡ等EDA軟件進行仿真,驗證了設計功能的正確性。

關鍵詞:FPGA;Verilog HDL;FIFO;數據采集

0 引言

隨著當今社會信息技術的快速發展,高速數據采集及處理在人們生活、現代工業和科學研究等很多領域中廣泛地應用。同樣,在一些高精度、快速的測量中需要對數據進行高質量、高速度的采集。傳統的數據采集系統往往采用單片機或數字信號處理器(DSP)作為控制器,來控制模/數轉換器(ADC)、存儲器和其他外圍電路的工作。但由于單片機本身的指令周期以及處理速度的影響,效率較低,很難滿足系統對數據采集系統實時性和同步性的要求。同時,FPGA具有高的時鐘頻率,運行速度快,開發周期短,集成度高,功耗低,設計費用低,組成形式靈活等諸多優點。因此,設計利用FPGA的高速實時數據采集系統有著重要的價值。

1 FPGA硬件設計

1.1 數字系統設計介紹

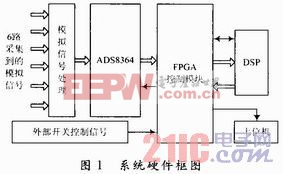

6路模擬信號經過模擬信號處理模塊,形成電壓差分模擬信號,其目的是減少直流漂移,去除共模干擾,為后級的模/數轉換器(ADC)做準備,系統的硬件框圖如圖1所示。經過ADS8364模數轉換器件后,將輸入的模擬差分信號變換為適用于控制過程、存儲、處理、執行計算并顯示讀出等其他目的的數字信號。在FPGA的控制下,數字信號被存儲在異步FIFO中,再按照設計要求將存儲在異步FIFO中的數據通過總線接口實時、高速、大量地傳輸到DSP芯片中進行實時處理,最后再傳輸到上位機。

1.2 外圍主要電路

1.2.1 外部開關控制信號

外部開關控制信號的作用是給整個系統提供開關信號。為了滿足工業應用,避免長線傳輸中的共地和電平不一致,采用了光電隔離,實現了將輸入的24 V電壓轉化為3 V輸出電壓的功能,然后再通過整形電路整形后,傳輸到FPGA的I/O接口上。

1.2.2 A/D轉換電路

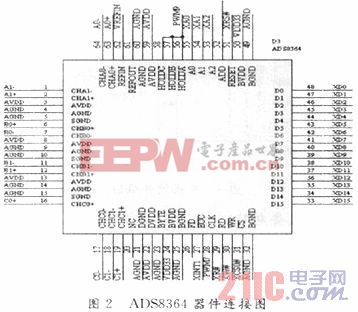

對于采集的6個通道的信號,由于采樣速率高,因此選擇了ADS8364芯片進行模數轉換。其工作電壓為+5V,獨立6通道全差分輸入,2.5V參考電壓的REFIN和REFOUT引腳、有效數據位為14位、采樣頻率可以根據設計要求進行調節并且最高的采樣頻率可以達到250 KSPS、帶有6級深度的FIFO輸出、功耗只有450 MW、6個差分采樣放大器以及高速并行接口等主要參數。

ADS8364芯片的輸入通道分為三組(A,B和C)的6路模擬信號輸入通道,每個端口含有ADCS和保持信號引腳,這兩個信號用來保證幾個通道能同時進行采樣和轉換,同時輸入電壓是從-VREF到+VREF之間變化的差分模擬輸入電壓信號。6個十六位ADCS可以同時工作,即6通道同時進行轉換。HOLDA,HOLDB,HOLDC這三個轉換保持信號啟動相對應的通道進行模數轉換。如果這些保持信號同時有效時,這6個通道轉換的結果就被保存在6個寄存器中,如果FPGA中的AD控制模塊對ADS8364芯片執行每一個讀操作時。ADS836就會輸出十六位數據到FPGA中,A0,A1,A2這3個是地址/模式信號,它們決定ADS8364芯片采用何種方式讀取數據。有單通道,單周期或FIFO模式三種模式供選擇。HOLDA,HOLDB,HOL DC至少20 ns保持低電平,相應的通道才能開始轉換。20 ns的低電平使得相應通道的采樣保持放大器處于保持狀態,進而所選擇的模數轉換通道就開始進行數據轉換,本設計方案所選擇的ADS8364地址/模式信號是單通道模式讀取數據,6通道同時進行數據轉換,其器件連接圖如圖2所示。

1.2.3 UART通信模塊

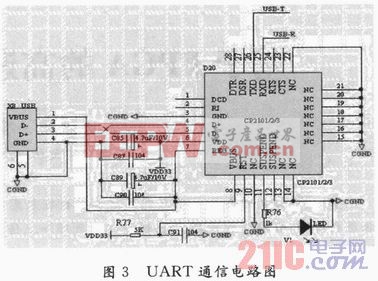

在本設計中,采用了一片CP2101芯片來實現與PC機的USB接口通信,其電路原理圖如圖3所示。

評論