基于FPGA的交通信號燈控制系統

摘要:為了解決傳統交通燈控制系統常采用單片機或PLC等控制芯片所具有的控制不精確、系統外圍電路復雜、程序修改不靈活、成本偏高等缺點,利用VHDL硬件描述語言,通過QuattusⅡ軟件和以CycloneⅡ系列FPGA為核心的開發板,完成交通信號燈控制系統的設計。該系統具有電路簡單、可靠性強、運算速度高、參數易修改等特點。通過軟件進行仿真,并在KX_7C5TP型開發板下載模擬,結果表明系統工作正常,控制器能完成預定的設計要求。

關鍵詞:交通信號燈控制系統;VHDL;EDA;FPGA

0 引言

隨著社會經濟的高速發展,由車輛大幅增加而帶來的交通問題日趨嚴重。因此,作為交通監管系統的重要組成部分,交通信號燈在協調人、車、路的關系時發揮著巨大的作用。

EDA(Electronic Design Automation,電子設計自動化)是依靠功能強大的計算機,對以硬件描述語言HDL(Hardware Description Langu age)為系統邏輯描述手段完成的設計文件加以處理,自動實現既定的電子線路系統功能的一種技術。利用EDA技術進行電子系統設計的最終目標是完成專用集成電路ASIC(Application Specific Integrated Circuit)的設計和實現。ASIC作為最終的物理平臺,集中容納了用戶通過EDA技術將電子應用系統的既定功能和技術指標具體實現的硬件實體。現場可編程門陣列FPGA(Field Programmahie Gate Array)是實現這一途徑的主流器件,其特點是具有極大的靈活性和通用性,開發效率高,成本低,技術維護簡單,工作可靠性好。

1 設計要求

1.1 應用背景

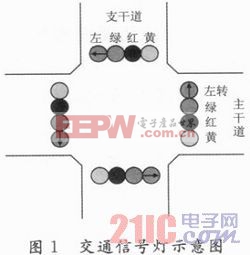

有一條主干道和一條支干道的匯合點形成十字交叉路口,主干道為東西向,支干道為南北向。為確保車輛安全、迅速地通行,在交叉道口的每個入口處設置了紅、綠、黃3色信號燈及左轉向燈,如圖1所示。

1.2 要求

(1)主干道綠燈亮時,支干道紅燈亮,反之亦然,兩者交替允許通行。主干道每次放行40 s,支干道每次放行30 s。每次綠燈亮,前10 s為左轉燈亮,后5 s為黃燈亮。余下為直行燈亮。

(2)能實現正常的倒計時顯示功能。

(3)能實現總體清零功能:計數器由初始狀態開始計數,對應狀態的指示燈亮。

fpga相關文章:fpga是什么

評論