基于FPGA的數據嵌入式圖像采集系統

根據I2C總線數據傳輸的時序,總線控制器的狀態機分為空閑狀態、啟動狀態、數據傳輸狀態、應答狀態和停止狀態。Idle狀態表示總線空閑狀態,SCL和SDA都為高電平,若clk=1則進入Start狀態。Start狀態表示總線啟動,此時保持SCL為高電平,將SDA由高電平變為低電平,從而啟動數據傳輸。Data_trans狀態中一次傳1 Byte數據。在本狀態中,1 Byte數據的傳輸過程為將時鐘線變為低電平,然后將數據放在數據線SDA上。再將時鐘線變為高電平,讓接收方進行數據接收。傳輸完1 Byte后進入Hold。Hold狀態用來表示應答階段,主要是產生一個時鐘脈沖,讓接收方對1 Byte的數據產生應答信號。在此狀態中進行對本次數據連續傳送是否完畢進行判斷。如未傳輸完則繼續到Start狀態進行下一次數據的傳輸,并將count-1。Stop狀態表示數據傳輸結束。在SCL高電平期間將SDA由低轉為高。然后輸出一個配置完成的信號。寄存器配置狀態機如圖3所示。本文引用地址:http://www.j9360.com/article/190003.htm

3.3 控制模塊

控制模塊由control_enable模塊和control_interface模塊組成主要負責圖像采集模塊和顯示接口模塊的同步和使能。當解碼芯片配置完成后,從CONFIGURACION_OK輸入使能信號,啟動該模塊,同時通過href和odd信號啟動圖像采集模塊和顯示接口模塊,href=1表示SAA7113H通過VPO傳輸像素數據;odd=1表示奇數場,odd=0表示偶數場。

3.4 像素存儲模塊

圖像的一幀為720×625提取其中的有效像素640×576存入SDRAM中,再讀出480行數據進行格式轉換和顯示。

由于SDRAM每個單元為16位,所以將一個Y和一個Cb或Cr合存在一個地址空間中,即兩個時鐘周期產生一個地址。SDRAM有4端口模式,2個用于將FIFO中的數據寫SDRAM,2個用于將數據讀到FIFO中,讀寫采用的時鐘不同,寫時鐘采用解碼芯片的27MHz,而瀆時鐘采用VGA的25MHz,由于SDRAM的讀寫速度為50 MHz,時鐘頻率不同,不能直接寫入,因此需要一個FIFO將數據暫時儲存,再將其寫到SDRAM中。

此處關鍵問題是隔行掃描到逐行掃描的轉換。SAA7113H是先奇數場后偶數場的順序輸出,即隔行輸出,而VGA顯示是逐行顯示的,因此要進行去隔行操作。利用對SDRAM的讀寫地址的控制能夠有效解決隔行到逐行的轉換問題,數據寫入SDRAM是將隔行數據寫入到SDRAM的0-640× 576的地址空間中,其中640×23-640×310為1、3、5、…奇數場的有效數據,640×336-640×623為2、4、6、…偶數場的有效數據。兩場數據分別通過不同的FIFO讀出,格式轉換時交叉讀取兩個FIFO中的數據,這樣讀出的數據即1、2、3、4、…逐行數據。

3.5 格式轉換模塊

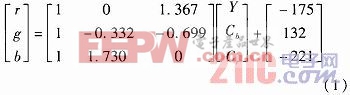

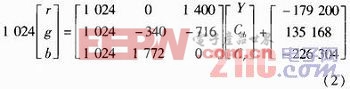

要將攝像頭采集的圖像顯示在顯示器上,需進行數據的格式轉換,將YUV格式的數據轉換成RGB格式的數據。YUV 4:2:2格式的數據兩個相鄰的像素共用一對Cb和Cr分量,所以在進行格式轉換時要先解交織,即一次從FIFO中提取相鄰的兩個像素數據,將Cb和Cr各復用一次,使得YUV變成4:4:4格式,然后進行格式的轉換。將轉換好的數據存放在reg_RGB中,VGA顯示的時候交叉讀取這兩個寄存器中的數據。轉換公式如下所示

由于在FPGA中進行浮點運算較困難,因此可將式(1)中的各系數轉化為整數在進行運算,采用將各系數放大1 024倍的方法,得到r、g、b后再除以1 024,放大后的公式為

根據上述公式得到r、g、b。然后將結果均右移10位完成除法運算,得到RGB值。由于r、g、b均為8位,取值范圍為0~255,而運算過程較易生成負數和超過255的正數,因此運算結果需將負數取0,超過255的正數取為255。此方法雖然會引入誤差,但對最終圖像的顯示效果不會有較大影響。

3.6 顯示接口模塊

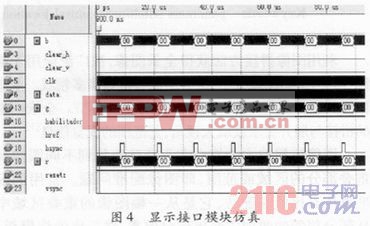

由interface_vga負責圖像的顯示,從reg_RGB寄存器中讀取轉換好的數據,對這兩個像素的讀取由一個轉換電路負責在兩個寄存器之間切換。顯示接口模塊將r、g、b以及hsync、vsync一起發送給編碼芯片THS8134,通過VGA顯示出來,hsync和vsyne分別是行和場同步信號。在仿真中,選用CycloneⅡEP2C20Q240C8芯片,用QuartusⅡ8.0進行綜合與仿真。圖4是對顯示接口模塊的仿真。由仿真結果可以看出,行同步和場同步符合時序要求。

4 結束語

實現了一種基于CycloneII系列FPGA與視頻信號處理芯片SAA7113H的嵌入式圖像采集系統。系統結構簡單系、統穩定、功耗低、成本低、速度快以及接口方便,可以滿足視頻監控系統等的需要。圖像采集系統中采用FPGA作為采集控制部分,可以提高系統處理的速度及系統的靈活性和適應性,對于不同的視頻圖像信號,只要在FPGA內對控制邏輯稍作修改,便可實現信號采集。

評論