基于FPGA的數字中頻接收和恢復系統設計

摘要 介紹一種數字中頻恢復系統,該系統分為光纖接收單元、FPGA核心單元和QDUC單元。光纖接收單元采用高速串行器/解串器TLK1501,完成高速串行數據的串行轉換。FPGA核心單元對數據進行解碼、檢驗、配置TLK1501和AD9957。QDUC單元實現基帶信號的上變頻和D/A轉換。測試結果證明,系統具有實時性好、工作穩定、抗干擾性強的優點。

關鍵詞 光纖傳輸;FPGA;數字上變頻器

直接數字頻率合成(Direct Digital Synthesizer,DDS)作為一種先進的信號產生技術,與傳統的頻率合成技術相比,DDS具有分辨率高、轉換速度快、功耗低和成本低等優點,經過40年的發展,已被廣泛用于數字信號處理、軟件無線電等領域。在現在的雷達系統中,高速高寬帶是現行的趨勢,傳統的并行傳輸技術由于存在碼間串擾、串音干擾和直流偏移等缺點,難以滿足高速高帶寬的傳輸要求。目前國內外有關雷達高速寬帶信號接收和恢復技術的研究很廣泛,多采用軟硬件相結合的設計方式,系統靈活,同時滿足信號實時輸出的要求。

文中討論的基于AD9957的多波形雷達信號恢復實現方案,融合了光纖通信、現場可編程門陣列(Field-Programmable Gate Array,FPGA)和DDS等技術,具有誤碼率低、抗干擾性強、實時性強、數字化、可編程和多功能等特點。

1 系統設計方案

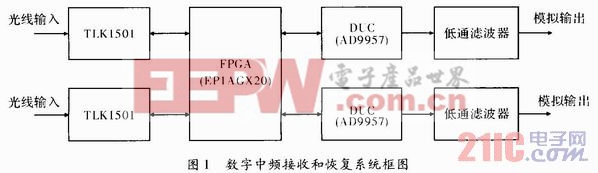

系統的設計結構如圖1所示。主要有光纖接收電路、FPGA單元、正交數字上變頻器(Quadrature Digital Up Conversion,QDUC)及信號調理電路組成。光纖傳輸的是已經被編碼、校驗、成幀后的數據,其接收電路主要由TLK1501電路完成,負責將光電轉換后的串行數據流轉換為并行數據。FPGA采用Altera公司帶有收發器的EP1AGX20CF48416N,完成光纖數據的解幀、校驗和解碼,剝離出有效的數據。同時,光收發器也可直接與FPGA連接,增強了系統的靈活性。正交數字上變頻器(QDUC)采用AD9957實現,完成基帶信號的數字上變頻(Digital Up Convei ter,DUC)和數模轉換(Digital Analog Converter,DAC)。信號調理電路將模擬信號濾波提純。

2 TLK1501接口設計

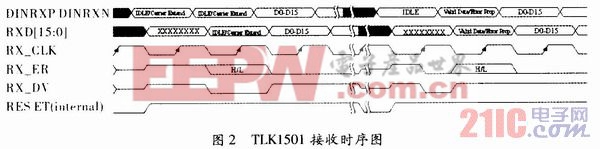

TLK1501是德州儀器推出的0.6~1.5 Gbit·s-1高速串行器/解串器,內部集成了8b/10b編解碼模塊。TLK1501有兩種工作模式,一是收發模式,二是只發模式。在收發模式下,TLK1501的發送和接收需要嚴格的同步,如果接收側斷開,則發送端自動發送同步碼,直到接收側重新同步。在只發模式下,TLK1501只是單向發送,接收端輸出為高阻態。在實際使用中,本系統用到了TLK1501的第一種工作模式,但只用到了TLK1501的接收數據功能。在接收數據時,TLK1501的DINRXP/DINRXN管腳上的高速串行數據流經過串并轉換和10b/8b解碼后恢復成16 bit并行數據,當RX_DV為高同時RX_ER為低時,在RX_CLK上升沿時,RXD[15..0]端口輸出有效數據。應用中TLK1501的接收時序如圖2所示。

評論