基于FPGA的IRIG-B編碼器的設計

我國靶場測量、工業控制、電力系統測量與保護、計算、通信、氣象等測試設備均采用國際標準IRIG-B格式的時間碼(簡稱B碼)作為時間同步標準。B碼是一種串行的時間格式,分為直流碼(DC碼)和交流碼(AC碼)兩種,其格式和碼元定時在文獻[1]中有詳細描述。本文介紹一種基于FPGA并執行IRIG-B標準的AC/DC編碼技術,與基于MCU或者DSP和數字邏輯電路實現的編碼方法相比,該技術可以大大降低系統的設計難度,降低成本,提高B碼的精確性和系統靈活性。

本文引用地址:http://www.j9360.com/article/189993.htm在此,組合GPS引擎和FPGA,得到B碼的編碼輸出,直接采用GPS引擎的100 pps信號觸發輸出B碼的每個碼元,利用從100 pps中恢復的1 pps信號提供B碼的時間參考點。DC編碼和AC數字調制均由純硬件邏輯通過查找表實現,它能使每個碼元的上升沿都非常精準,都可以作為百分秒的時間參考點,而計時鏈的預進位功能則保證了絕對時間的精確,不僅可以滿足實時系統對時間同步,還可以實現多節點的數據采集嚴格同步,為分析和度量異步發生的事件提供有方的支持。

1 IRIG-B編碼格式

IRIG標準規定的B格式碼如圖1所示,每秒鐘發1次,每次100個碼元,包含1個同步參考點(Pr脈沖的上升沿)和10個索引標記。碼元寬度為10 ms,用高電平寬度為8 ms的脈沖表示索引標記,用寬度為5 ms的脈沖表示邏輯1,用寬度為2:ms的脈沖表示邏輯0。

如圖1所示,交流碼的載波是1 kHz正弦信號,幅度變化峰一峰值范圍為0.5~10 V。調制比為U1/U0=1/6~1/2,即邏輯1是5個幅度為U1的1 kHz正弦信號,邏輯0是2個幅度為U1的1 kHz正弦信號,索引標記是8個幅度為U1的1 kHz正弦信號,其他時間是幅度為U0的1 kHz正弦信號。

2 系統方案

2.1 系統原理框圖

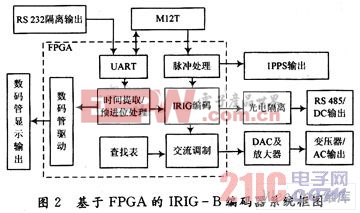

設計授時系統需要一個精準時基。在此利用精密授時型GPS引擎M12T作為系統時基,利用AlteraFPGA檢測M12T輸出的百分秒(100 pps)同步信號和經串口輸出的絕對時間信號,編碼后輸出到DC/AC接口模塊,再輸出到物理鏈路,系統結構圖如圖2所示。

上述系統首先實現了B碼直流編碼,而后在直流碼的基礎上實現交流調制,以得到交流碼,同時提供恢復每秒脈沖數輸出和隔離RS 232串行口輸出且符合Motorola格式的時間碼,以及數碼管的時間顯示。時間顯示部分用FPGA實現比較簡單,下文不再詳述。

評論