基于FPGA的簡易微型計算機結構分析與實現

引 言

本文引用地址:http://www.j9360.com/article/189850.htm通常,人們對微型計算機的工作原理及硬件結構的了解來源于書本知識,深入理解掌握其功能特點比較困難,要自己親手去做一個類似功能的微型計算機更是不可能。隨著可編程邏輯器件的廣泛應用,為數字系統的設計帶來了極大的靈活性,用戶可以利用FPGA(現場可編程門陣列)來開發出一個精簡指令的CPU,同時對微型計算機的原理及結構進行充分研究,便于將來進行相關ASIC(專用集成電路)設計,也可用于計算機原理教學之中。

1 微型計算機結構及原理

以一個簡化的微型計算機為例,微型計算機的簡化結構。

1.1 微型計算機結構

微型計算機由PC(程序計數器)、IR(指令寄存器)、CON(控制部件)、MAR(存儲地址寄存器)、ROM(只讀存儲器)、A(累加器)、ALU(算術邏輯部件)、B(寄存器)、OUTREG(輸出寄存器)、DLEDDIS(數碼管動態掃描模塊)及DECL7S(顯示模塊)等組成。這里僅介紹有所改變或不同的模塊,其余可見文獻[1]。

L為數據載入控制信號,E為三態輸出選通信號,clk為時鐘信號,clr為清零信號,Cp為控制PC加1信號,S0-S3為控制ALU進行加減或邏輯運算的選擇信號。所有的控制、時鐘及清零信號由CON模塊給出,而CON模塊由外部時鐘clkin及清零信號rst控制。PC可以置數,即可執行跳轉指令。OUTREG可清零,便于多次調試。DLEDDIS及DECL7S用來把地址及結果在數碼管上顯示出來。

1.2 微型計算機原理

雖然這臺微型機可以實現16條指令,但本文對指令不做擴展,僅以5條指令為例。LDA為將數據裝入累加器A(操作碼0000);ADD為進行加法運算(操作碼0001);SUB為進行減法運算(操作碼0010);OUT為輸出結果(操作碼1110);HLT為停機(操作碼1111)。

在程序和數據裝入后,當外部給出時鐘信號及清零信號無效時,由CON模塊發出信號及控制字,開始取出和執行每條指令。如控制字順序為ErLrS3S2S1SOEuLm LbEaLaEi LiCpEpLp,這里Lr可用于存儲器為RAM時做寫使能信號。由于采用的是數據總線與地址總線合一的總線結構,一條指令的執行需要6個機器節拍,即前3節拍取指周期與后3節拍執行周期。如執行ADD 0AH,機器碼為1AH(0001 1001)。第1節拍將PC內容送入MAR,控制字為“0000 0001 00000010”,即Ep與Lm為1;第2節拍將ROM中對應地址單元中的內容送到IR,IR高4位送至CON,控制字為“1000 0000 0000 1000”,即Er與Li為1;第3節拍使PC加1,控制字中Cp為1,其余為0;第4節拍將IR的低4位送至MAR,Ei與Lm為1;第5節拍將ROM中的內容送入累加器A中,Er與La為1;第6節拍為加法運算,Eu與La為1,同時S0-s3選擇為加法運算。

2 FPGA實現

2.1 總線方式

總線方式是指嚴格按圖1用FPGA實現相應結構的微型機。本實驗采用上海航虹公司的AEDK實驗箱,FPGA芯片為Altera公司的EPF10K20TC144-4,軟件采用QuartusII4.0、Max+plusII10.0及synplifypr07.5,程序設計采用VHDL語言。

共有11個子模塊,最后用元件例化語句構成總模塊。以設計程序計數器模塊C-PC及控制模塊C_CON為例簡單做一介紹。

當三態輸出信號es選通時,即es=“1”,PC可輸出,否則輸出為高阻態。數據或地址與總線相關的子模塊都需采用三態門。由于采用了三態門,最好用QuartusⅡ軟件來進行編譯,Max+plusⅡ有時不一定可以通過。

用synplify pro7.5對C_PC模塊進行RTL(寄存器傳輸級)原理圖觀察,如圖2所示。其綜合電路與一個4位二進制計數器類似,只是多了一個三態門。用synplify pro7.5不僅可以觀察RTL電路,還可以觀察門級電路結,深入了解其內部結構。

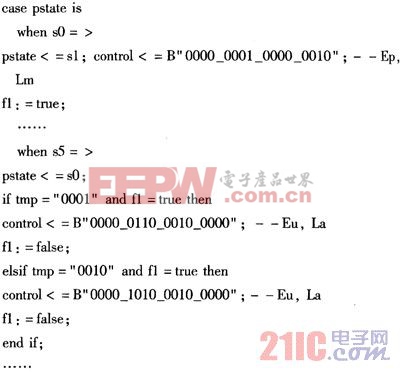

C_CON模塊是最關鍵的模塊,因為所有的控制信號都由它發出。由于指令執行需6個機器節拍,每個節拍對應相應功能,采用狀態機是實現此高效率、高可靠邏輯控制的重要途徑。如以下程序所示,每個狀態對應著不同的控制字,共有6個狀態。

只讀存儲器模塊可使用LPM_ROM的LPM_FILE文件,便于調試不同的程序。

評論