從Multicore到Many-Core:體系結構和經驗

您可能已經習慣了芯片系統(SoC)的multicore處理器這一概念,而現實卻總是在不斷變化。8月份舉行的Hot Chips大會研討中,已經清楚的表明multicore正在向many-core發展:在SoC核心位置,密切相關的處理器內核的數量在不斷增長,從2個或者4個增加到8個、16個,甚至是很多,很多。

本文引用地址:http://www.j9360.com/article/189778.htm這種增長僅是摩爾定律發展的另一階段,系統開發人員還是能清楚的了解這一切嗎?從multicore發展到many-core是類型的變化,還是僅僅是規模的變化?這種轉變能解決系統開發人員面臨的問題嗎?

為找到這些問題的答案,我們與一些團隊進行了交流,他們已經在many-coreSoC開發上積累了一些設計經驗。我們向他們提出了一個簡單的問題:您的體驗與使用multicore有什么不同嗎?對于這一簡單的問題,我們得到了各種各樣的回答。

Many-core的發展

Hot Chips的論文列出了SoC體系結構向many-core領域發展的三條主要路線。我們從Cavium的Kin-Yip Liu在小規模無線基站SoC設計論文中闡述的路線開始,這些設計包括微基站、微微基站和毫微微基站。

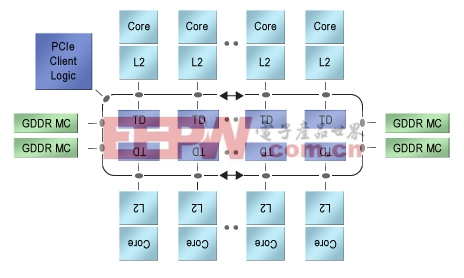

名為Octeon Fusion CNF71xx的設計如 圖1所示,包括兩個處理簇,含有四個一組的增強MIPS64內核,以及圍繞一個共享L2高速緩存的各種硬件加速器,還有6個為一組的數字信號處理(DSP)內核,每個內核都有很多硬件加速器,這些內核分布在共享存儲器交換架構周圍。

圖1.Cavium的Octeon Fusion體系結構結合了CPU簇以及相連接的硬件加速器和分立的DSP內核簇。

四個CPU還很難說明是many-core設計。但是有兩個很好的理由讓我們的討論從這一芯片開始。首先,增加6個DSP內核使得芯片成為10核異構體系結構,表面上看已經進入many-core領域。其次,更多的是在理論上,Cavium使用內核的方式與傳統的multicore并不相同。

Multicore SoC將線程映射至內核的方式一般是靜態的。而隨著內核數量的增加,這種映射更具流動性。CPU和DSP可以按數據流來劃分,也可以構成虛擬流水線,每一個完成復雜任務的幾級任務。或者,處理器可以觀察任務序列,一旦空閑,就可以執行新任務。不斷增強一個處理器的能力來完成所有數據的處理,而這一概念正在轉向由很多處理器共同完成一項工作——從固定硬件到軟件與加速器的組合。這種概念上的變化確定了multicore與many-core計算之間的邊界。我們看到這種變化是從本地對稱的Octeon Fusion體系結構開始的。Cavium很顯然同意這一觀點。他們在Hot Chips上的研討表明,目前的芯片只是軟件兼容系列的開始,這些系列能夠從單核發展到48核。

作為對比,Fujitsu的Takumi Maruyama發表的論文介紹了公司的16核芯片SPARC64 X將成為服務器中心處理器。SPARC64 X與Octeon共享了一個重要的體系結構概念:16個SPARC內核簇圍繞一個大規模內核——24 Mbyte,共享L2高速緩存。但這也有很大的不同。這就是專用硬件加速器。Fujitsu將其稱之為“芯片軟件”。Fujitsu沒有在CPU之外開發松耦合加速器,來處理棘手的運算問題(在這個例子中,十進制數學運算、加密和數據庫函數等),而是開發了新的RISC類型指令來加速這些運算,在每一CPU的浮點單元流水線中增加了必要的執行硬件。因此,硬件加速并不能靈活的共享L2高速緩存,或者鏈接系統總線,而是成為CPU不可缺少的組成部分。實際上,這些加速器增加了指令,編譯器可以將其優化到CPU指令流中。

Intel和many-core

最后,考慮Intel的Xeon Phi,或者還可以考慮Intel資深首席工程師George Chrysos所介紹的Knights Corner,如 圖2 所示。在Chrysos有些含糊的描述中,該器件是采用了“50多個”x86處理器內核的協處理器,還含有四個GDDR存儲器控制器,以及與主處理器Xeon CPU連接的PCI Express® (PCIe®)接口。每一個處理器都有自己的專用矢量處理單元,以及自己的512 Kbyte L2高速緩存。L2高速緩存、GDDR控制器以及PCIe控制器不是由傳統的交換矩陣連接的,這樣會導致規模非常大而在物理上無法實現,而是由雙向環形總線連接。這一總線在每一方向上都有64字節數據通路,通過分布式標簽方案來實現所有L2之間的一致性。遵從體系結構的發展規律,Xeon Phi在內部與早期的multicore設計非常相似,即,在PlayStation 3中首次使用的IBM Cell協處理器。

圖2.Intel的Xeon Phi是50多個x86內核構成的異構陣列,這些內核通過兩路跑道型互聯結構連接起來。

Xeon Phi代表了從multicore向many-core的深入發展。這里,與Cell不同,沒有專門的加速器或者專用存儲器結構,只有相對簡單的x86處理器,連接了矢量處理單元和高速緩存、DRAM控制器以及PCIe接口。所有這些芯片都專門用于執行x86指令代碼。Intel展望了Xeon Phi將用于物理、化學、生物和金融分析等應用中。

評論