基于FPGA的等精度頻率計的設計與實現

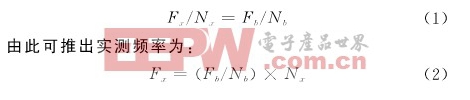

設在某一次預置門控時間Tc中對被測信號計數值為Nx,對標準頻率信號的計數值為Nb,則根據閘門時間相等,可得出公式(1):

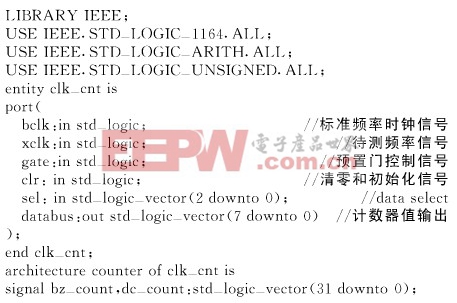

2 頻率計的VHDL設計

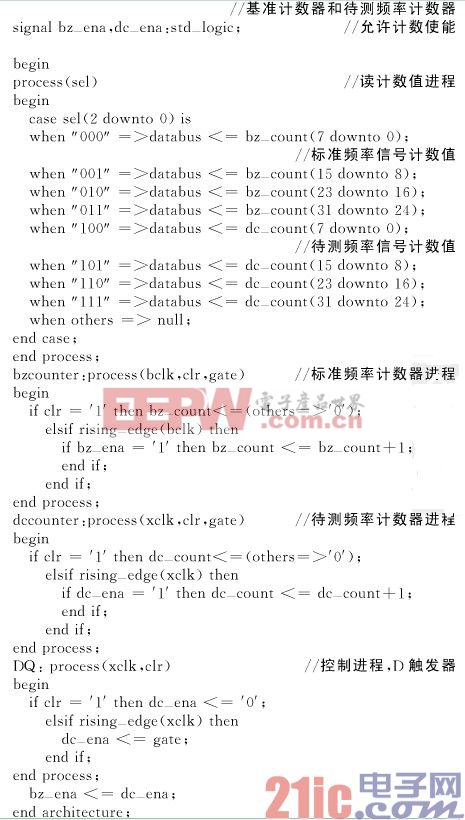

本設計采用ALTERA公司的FPGA芯片EPF10K10,該芯片管腳間的延遲為5 ns,即頻率為200 MHz,應用標準化的硬件描述語言VHDL有非常豐富的數據類型,他的結構模型是層次化的,利用這些豐富的數據類型和層次化的結構模型,對復雜的數字系統進行邏輯設計并用計算機仿真,逐步完善后進行自動綜合生成符合要求的、在電路結構上可實現的數字邏輯,再下載到可編程邏輯器件中,即可完成設計任務。下面給出該頻率計基于EPF10K10的VHDL描述源程序:

評論