基于FPGA的相關測速系統

相關測速是以隨機過程的相關理論和信息理論為基礎發展起來的[1-2],它的應用始于上世紀40年代,首先應用于軍事上,然后逐漸轉移到科學研究和民用上,現在已經在各個領域內得到日益廣泛的應用。

本文引用地址:http://www.j9360.com/article/189729.htm盡管相關測速的運算量非常巨大,但是隨著EDA技術的高速發展,大規模可編程邏輯器件CPLD/FPGA的出現,集成電路做得比以前更快、規模更大。設計人員有很大的自由度去設計實現用途專一的集成化數字電路:在實驗室里,在電腦系統前,現場設計、現場編程、現場配置、現場修改和現場驗證,從而在現場實現數字系統的單片化設計和應用。這意味著無需更改電路,只要改寫FPGA內部功能,整個系統即可實現新功能,即一個最小的芯片方案可以轉換來執行多個功能,硬件的配置變得如同軟件一樣靈活方便,而其速度和集成度,也隨著VLS工藝的發展而迅速提高,這就為相關測速的實際應用提供了硬件平臺。只要找到合適的算法并建立相應的硬件處理系統,運算速度和精度就能達到預期的要求。

1 系統硬件及相關算法的確定

本文測速的原理是:以CCD攝像頭作為前端裝置,將CCD攝像頭所采集的圖像信息送到FPGA中,由FPGA對其進行處理,并給出當前運行的速度。在滿足速度上限的條件下,連續兩次采集的圖像必然有重疊的部分。對連續兩次的圖像進行相關處理,就可以得到它們之間的位置關系,再結合采樣間隔時間,從而可以得出速度。

由于圖像處理算法涉及的運算量比較大,對系統的快速處理能力和大數據量的吞吐能力有嚴格的要求[3],因此系統中的核心器件FPGA的選擇必須遵循以下原則:(1)調試使用方便;(2)適當的響應速度;(3)適當夠用的邏輯資源;(4)足夠的輸入輸出(I/O)端口。

根據系統要求,本文采用Altera公司的超大規模可編程邏輯器件Cyclone II[4]。Cyclone II系列FPGA是繼Cyclone系列低成本FPGA在市場上取得成功之后,Altera公司推出的更低成本的FPGA。Altera采用相同的方法在盡可能小的裸片面積上構建了Cyclone II系列,擴展了低成本FPGA的密度,最多達68 416個邏輯單元(LE)和1.1 Mbit的嵌入式存儲器,從而可以在低成本的FPGA上實現復雜的數字系統。優異的性價比使CycloneII系列FPGA可以廣泛地應用于汽車電子、消費電子、音/視頻處理、通信以及測試測量等終端產品市場。

在測速系統的設計中,假設攝像頭采集到的原始圖大小為1 280×1 024,為了保證采集的圖像背景區域能夠有明顯的目標,比較理想的情況是將模板區域取得越大越好,將目標全部包括在內[5-6]。當搜索區域大小為m×m, 模板大小為n×n時,歸一化互相關算法所需的運算次數約為(5n2+9)×(m-n+1)2次,計算量巨大。如果采用512×512大小的搜索區域,模板采用32×32大小,運算乘加次數近12億次,硬件將無法提供足夠的乘加器。如果采用128×128的搜索區域和32×32的模板,圖像的檢索區域比較小,測速的范圍會比較低,精度也會下降。綜合考慮攝像頭采集圖像的范圍和精度,并且充分利用硬件所能提供的內部存儲單元,本文將搜索區域設定為256×256,模板大小設定為32×32,如圖1所示。

2 測速系統的構成及設計

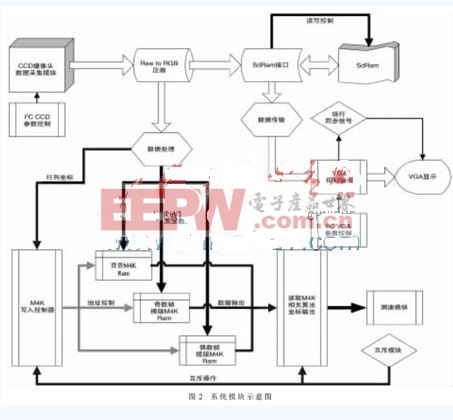

根據所需的功能,將系統劃分為以下幾個模塊,分別加以實現。如圖2所示。

(1)CCD攝像頭數據采集模塊

攝像頭采集的數據需要有圖像幀和消隱幀。當前幀是圖像幀時,讀入圖像的行數據,讀入1 280×1 024個數據后,列計數X_Cont和行計數Y_Cont歸零。消隱幀時不輸出。

評論