基于FPGA和DSP的微振動傳感器信號采集系統設計

為了避免系統重置之前half_full信號上升沿導致錯誤的觸發DSP的EDMA事件,在rst置位之前half_full置1。模/數轉換模塊的AD9235輸出位數是12位,FIFO的輸入和輸出均設為12位。本文引用地址:http://www.j9360.com/article/189702.htm

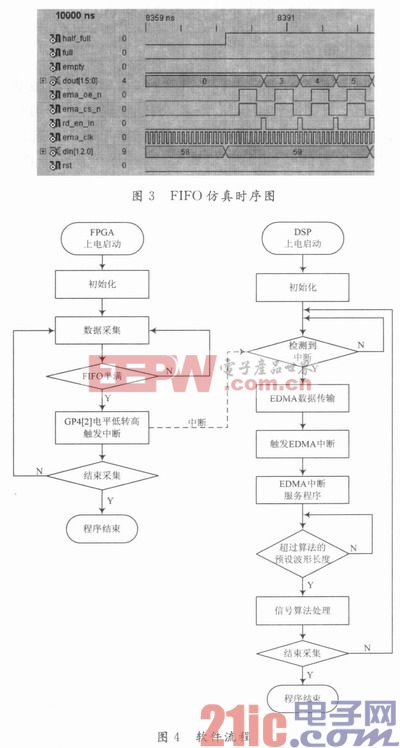

3.2 DSP的軟件流程

DSP模塊的軟件流程設計采用TI的DSP集成開發環境CCS3.3。DSP中的軟件配合FPGA上的FIFO一起控制信號的采集和數據的實時處理。軟件實現的功能分3個部分:系統初始化,EDMA傳輸控制和中斷服務程序,算法處理。軟件流程圖如圖4所示。

C6747上電后,首先進行系統初始化,設置各配置寄存器使DSP各功能模塊按設計要求運行,主要配置管腳復用、PLL、PSC和EMIF。FPGA同時啟動并開始控制AD9235開始采集數據,傳感器的信號經過模/數轉換進入FPGA的FIFO緩沖器,當FIFO內的數據量達到設定長度時,half_ full信號線電平由低轉高,輸出中斷信號。然后,因為此信號線和DSP的通用管腳GP4[2]相連,DSP內部的EDMA3控制器會檢測到此GPIO中斷事務,并產生一個傳輸請求,按照設定的參數把數據從FPGA內的輸出FIFO轉移到DSP模塊的SDRAM存儲器。在完成此EDMA傳輸請求之后觸發一個EDMA中斷,在中斷服務程序中檢測SDRAM內數據長度。最后,當SDRAM內存儲的數據長度達到設定的長度時,觸發信號處理函數進行信號處理,譬如對信號進行濾波、小波變換、功率譜分析等。

4 結語

本文基于FPGA和DSP,針對M—Z型光纖微振動傳感器設計了一種結構簡單、低功耗、實時性能好的信號采集和算法處理的實時系統。測試結果表明系統能采集傳感器信號,準確傳輸到DSP。并進行算法處理;為光纖微振動傳感器的數據采集和處理提供了一個良好的解決方案。該系統基于FPGA和DSP,能適應不同的算法,有利于系統的擴展和改進。

fpga相關文章:fpga是什么

傳感器相關文章:傳感器工作原理

干涉儀相關文章:干涉儀原理

光纖傳感器相關文章:光纖傳感器原理

評論