FPGA程序遠程在線更新設計

1 概述

本文引用地址:http://www.j9360.com/article/189689.htm現場可編程門陣列(Field Programmable Gate Array,FPGA)器件具有高密度、低功耗、高速、高可靠性等優點,在航空航天、通信、工業控制等方面得到了大量應用。FPGA的處理器分為軟核和硬核,并且軟核處理器具有高度的靈活性和可配置性。

由于FPGA器件采用的是SRAM工藝,在斷電的情況下FPGA內的配置數據將丟失,所以需要非易失的存儲器來結合FPGA完成嵌入式系統的設計。EPCS(Erasable Programmable Configurable Serial)Flash屬于串行接口Flash,具有接口簡單、體積小、配置方便的特點,通常用來存儲FPGA的配置文件和Nios II的軟件可執行代碼。在經過合理的配置后,系統在上電后就可以從EPCS Flash中讀取這些文件來啟動整個系統。

為了能使系統得到更靈活的應用,充分發揮FPGA的靈活性、高效性,FPGA的軟硬件程序都需要方便的更新和升級功能;而當形成產品后,通過JTAG和Nios II IDE工具來聯合完成對EPCS Flash的更新燒寫很不方便。為此,本文結合Altera公司提供的工具,提出了一種遠程在線更新FPGA配置文件和Nios II程序文件的方法。

2 系統硬件結構

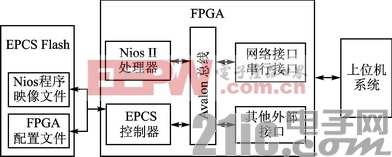

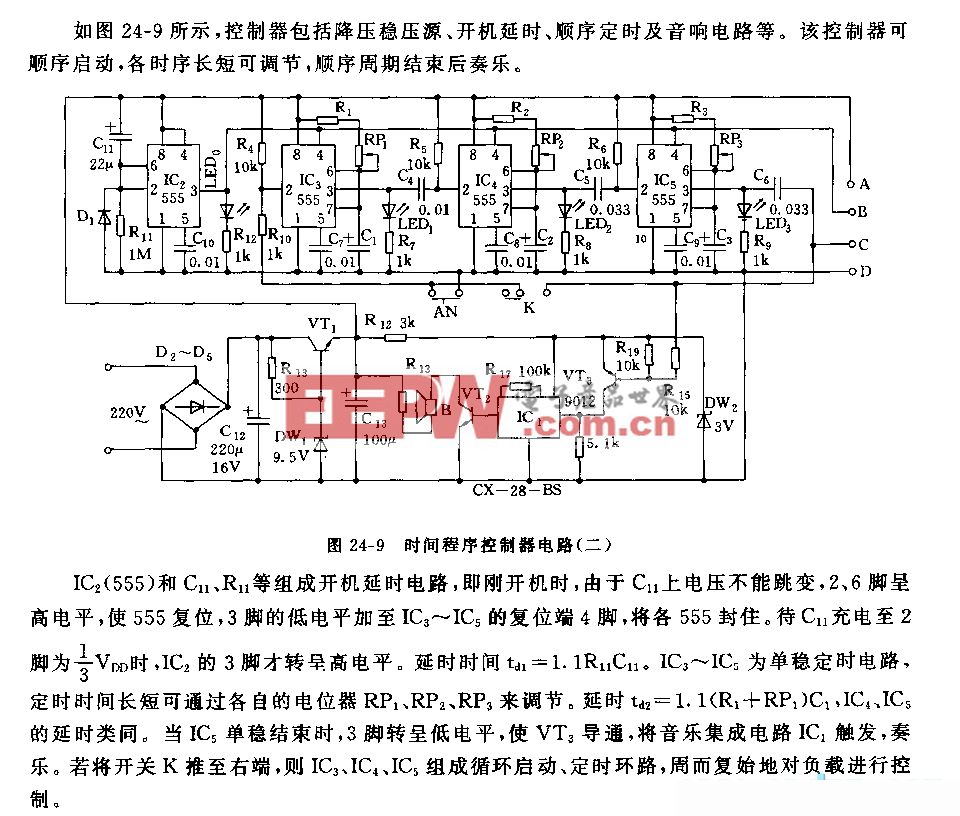

系統硬件結構如圖1所示。

圖1 系統硬件結構圖

系統主要有上位機系統、FPGA系統、EPCS Flash三個主體部分。上位機系統提供人機交互的部分,FPGA系統包括Nios II處理器、EPCS控制器、網絡及串行接口和其他外部接口,EPCS Flash主要用于存儲FPGA的配置文件和Nios程序映像文件。上位機系統通過FPGA集成的網絡及串行接口來完成通信工作。

FPGA采用Altera公司的Cyclone III系統的EP3C40F484I7N芯片。它具有低功耗、高集成度、易于使用的特性。EPCS Flash采用Altera公司的EPCS16SI16N芯片,它支持多種可配置的時鐘源,最高支持100 MHz的外部時鐘源,具有16 Mb的存儲空間,足夠滿足一般的FPGA配置文件和Nios程序文件的存儲需要。

3 更新程序處理流程

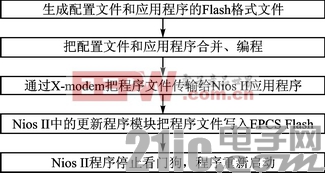

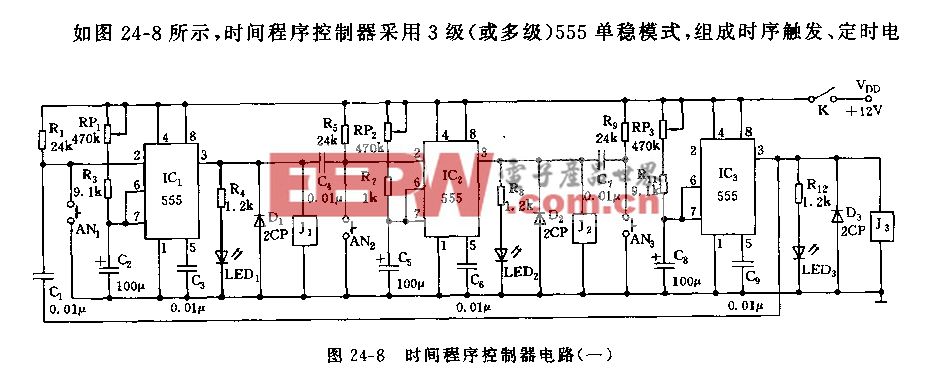

更新FPGA的配置文件和Nios II的應用程序的流程如圖2所示。

圖2 更新程序處理流程

本方法把由Nios II IDE生成的FPGA配置文件和Nios II程序文件合并,并編程為一個可以直接執行的、包含FPGA配置文件和Nios II程序文件的二進制BIN文件。然后把該文件通過Xmodem協議由上位機系統傳輸給Nios II的應用程序。Nios II的應用程序接收到完整的BIN文件后,把該BIN文件寫入到EPCS Flash中。最后,Nios II的應用程序停止看門狗,程序重新啟動,即完成了FPGA的遠程在線更新程序的過程。

評論