基于SOPC的異步串行通信IP核設計

隨著嵌入式技術的發展,基于SoPC技術的嵌入式系統所具有的軟硬件可裁減、可擴充、可升級以及可在線修改的特點越來越受到人們的重視。SoPC系統通常具有以下基本特征:采用大容量可編程邏輯器件來實現,單芯片、低功耗;至少包含1個以上的嵌入式處理器IP核;具有一個或多條片上總線作為系統擴展功能的接口;具有充足的片上可編程邏輯資源,用戶可以根據需要擴充功能部件。

本文引用地址:http://www.j9360.com/article/189686.htm異步串行通信協議(UART)以低成本、高可靠性等優點而廣泛應用于嵌入式系統中,多篇文獻也討論了UART協議的硬件設計方法,但多數只限于討論UART協議的硬件實現,缺少從SoPC系統的角度論述UART IP核的設計方法。本文以UART IP核和PLB總線為例,討論了在SoPC系統下UART IP核的設計方法,該方法對其他IP核的設計有一定的參考作用。

1 UART協議介紹

UART是一種串行異步通信方式,它采用RS232電平在串行鏈路上進行全雙工的通信,其數據傳輸格式如圖1所示:UART協議在空閑時為高電平,通過發送起始位提示接收方數據傳輸即將開始,接著傳輸8位有效數據位和奇偶檢驗位,最后發送停止位表示一個字符傳輸完成。

2 SOPC UART通信系統介紹

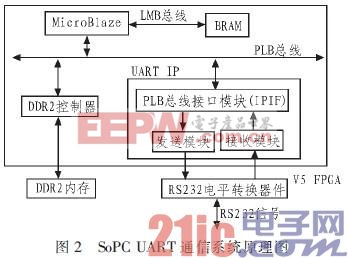

本文設計的SOPC UART通信系統主要包括MicroBlaze處理器、PLB總線、UART IP核和DDR2控制器IP核,如圖2所示。

MicroBlaze處理器是Xilinx公司針對其FPGA器件優化的32位微處理器核,它采用RISC(Reduced Instruction System Computer)架構和哈佛總線結構,具有獨立32位數據和指令總線,能夠高速執行和訪問片上存儲器和片外存儲器上的程序與數據;提供本地塊存儲器總線(LMB)、處理器本地總線(PLB)等總線接口。

PLB總線作為IBM CoreConnect總線協議簇中的一部分,廣泛的應用于IBM PowerPC處理器架構中。該總線具有總線地址空間大,總線吞吐率高,能支持多個主從設備連接等特點。如圖3所示,MicroBlaze處理器通過PLB總線與UARTIP核、DDR2控制器相互連接,各部件之間通過PLB總線協議進行交互。其中,MicroBlaze處理器作為主設備完成系統控制和UART通信流程控制,UART IP核作為從設備在主設備的控制下完成異步串行通信,DDR2存儲指令和數據。

MicroBlaze處理器和DDR2控制器采用Xilinx公司提供的IP核,UART IP核由用戶編寫邏輯,它是文中設計的主要內容,對此模塊的設計將在下一節進行詳細闡述。

評論