基于SoPC和NIOS Ⅱ的SD卡文件系統的設計與實現

SD卡中的數據是以塊為單位進行存儲的,如果在硬件層面對其進行操作,則不僅要非常了解SD卡的數據存儲結構,還要對FAT系統有深刻的理解,然后用復雜的時序狀態機對其扇區進行初始化和讀取控制,對硬件直接進行操作可以節省FPGA資源。為了更有效地組織和管理SD卡中的數據,必須采用文件的格式進行組織數據,這就要求在SD卡中內嵌文件系統[1]。而隨著FPGA的高速發展,以AlteraNIOSⅡ和Xilinx的MicroBlaze為代表的軟核處理器以其高可定制性、與ARM相比相同價格下的高性能得到廣泛的應用。

本文引用地址:http://www.j9360.com/article/189683.htm本文正是利用其豐富的外設和接口定制構建SD卡的FAT文件系統。

1 接口和控制器的設計

1.1 接口的配置

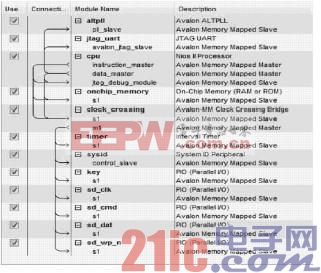

SD卡有SD模式和SPI模式2種,SPI是一種高速、同步、全雙工的通信總線,只占用4根信號線,節約芯片的管腳,有利于PCB的布局。前者速度較快,后者比較方便我們采用后者SPI與FPGA進行通信,它由4個信號組成,分別是CS(片選信號)、MOSI(主機到SD卡)、MISO(SD卡到主機)、SCLK(主機和SD卡的同步時鐘),以主從方式工作,本文中SPI為主機,SD卡是從機,處于單主單從模式。在由NIOSⅡ軟核處理器控制的Avalon總線[2-3]下可以方便地與SD卡進行對接。Avalon總線是一種將片上處理器和外設連接成片上可編程(SoPC)的一種簡單總線結構,它規定了主從設備之間的結構方式及其通信方式,通過使用SoPC Builder可以很方便地將自定義外設和其他組件組合起來,生成按照組件例化的系統模塊,并自動生成內部總線邏輯,自動完成外設和存儲器的地址映射、中斷控制和總線控制。圖1所示為設備之間的連接示意圖,NIOSⅡ處理器和外設SD卡控制器的通過Avalon總線結構進行數據交換和溝通,SD卡控制器控制著外部SD卡存儲介質。

1.2 控制器的設計

SD卡控制器[4]是FPGA和SD卡之間進行通信的翻譯官,主要實現3大功能:(1)復位和初始化SD卡。控制器按照SD卡總線協議產生控制時序對其進行復位和初始化。

(2)讀寫SD卡。控制器通過CMD線發送讀或者寫的命令以及SD卡扇區地址,確認收到正確的響應后,通過DAT線進行讀和寫操作(分別涉及串并轉換和并串轉換),一次傳輸一個扇區的數據(512B),傳輸完畢后將就緒信號置為有效。

(3)設置SD卡。通過CMD線發送命令和參數,不發送或接受數據。

圖1設備連接示意圖

1.3 SoPC中的硬件搭建

SoPC(SystemonaProgrammableChip),即可編程片上系統,用可編程邏輯把整個系統放到一塊硅片上,是一種特殊的嵌入式系統,可以編程的片上系統(SOC)[5]。

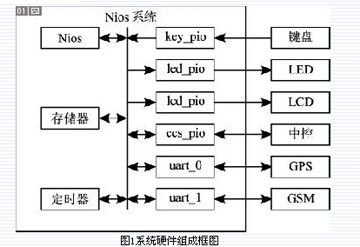

借助于AlteraSoPC方便的組件定制、硬件組裝和它的靈活的設計方式,不用一個個親自用硬件語言去實現各個組件,只需要在SoPC里定制,最后結果如圖2所示,因為SD卡的工作頻率最高為25MHz,與FPGA自身的時鐘頻率不一定一樣,所以要加上clock_crossing用于協調2個不同的時鐘域。onchip_memory是片內存儲器,用于儲存程序運行的代碼或者堆棧之類的變量。timer和sysid用來協調這些組件良好運作,例如SoPCBuilder會使用SystemID為每個系統提供識別符號,NIOSⅡEDS可以用此防止使用者燒錄與硬件信息不符合的sof文件。Timer是內部時鐘定時。如果丟失這兩個組件,會導致最后的軟件運行出現錯誤。

圖2SoPC組件定制

其中sd_wp_n是SD卡寫保護信號線,由于默認激活SD卡所以片選信號沒加。altpll是鎖相環,用來調節穩定所需的時鐘信號,DE2系列的開發板上都有1到2個鎖相環。jtag_uart用來調試、打印數據到控制臺,驗證讀取寫入的數據是否相同。

評論