基于FPGA的應力應變信號監測系統的研究設計

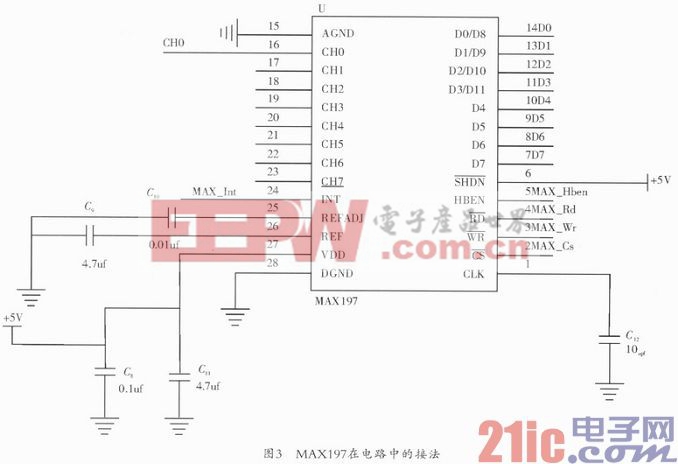

MAX197工作時,參考電壓可以由片內提供或片外輸入,視實際需要而定,當使用片內參考電壓時,可在REFADJ端和REF端分別獲得精度為±1.5%的參考電壓2.5V和4.096V。當使用外部參考電壓時,參考電壓可以分為從REF或REFADJ輸入當從REF輸入時,只要把REFADJ和VDD相連,并在輸入端REF和地之間加接一個4.7μF旁路電容;當從REFADJ輸入時,只要REF端通過4.7μF電容旁路到地,并在輸入端與地之間接一個0.01μF旁路電容,這種輸入方式可以省掉外接緩沖放大器,MAX197的電路接法如圖3所示。本文引用地址:http://www.j9360.com/article/189659.htm

4 基于FPGA的控制模塊的設計:

本設計利用SOPC技術存FPGA內部集成Nios II嵌入式處理器作為控制模塊,可以像單片機一樣用C語言對其進行編程開發,易于實現復雜功能,而且使用Nios II開發時可以根據實際情況選擇所需的PIO和外設數量,定制出所需的系統,避免資源浪費,降低系統功耗。

4.1 Nios II軟核的搭建

首先需要添加的是CPU,NiosII軟核為用戶提供了三種具有不同功能的CPU配置。本系統選擇Nios II/f類型,對系統所需CPU的性能和邏輯資源的占用率進行了平衡。

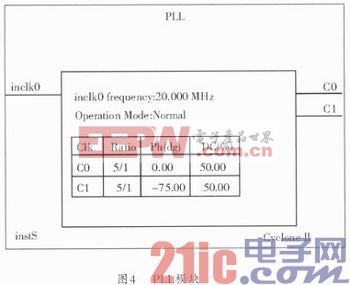

4.2 建立鎖相環PLL模塊

搭建好軟核之后還需要建立一個鎖相環,對時鐘進行倍頻.由于前期所用的開發板上是20MHz的有源品振,需要將其倍頻到100MHz以滿足之前搭建的軟核的時鐘,還需要為SDRAM提供100MHz的時鐘,在Quartus II9.0中用HDL語言設計生成的A/D控制模塊如圖4所示。

fpga相關文章:fpga是什么

評論