基于FPGA的雙備份多路數據采集存儲系統的設計與實

隨著信息技術的發展以及數字集成電路速度的提高,實時處理大量數據已經成為現實,但在一些特殊條件下,無法實時傳輸數據,必須使用存儲測試方法。該方法是在不影響被測對象或在允許的范圍下,將微型存儲測試系統置入被測體內,現場實時完成信息的快速采集與存儲,并回收存儲器,由計算機處理,再現被測信息的一種動態測試技術[1]。實際應用中,由于在不同的條件下對采樣速率和采樣精度的要求有所不同,系統的實現方法也各有特點。為了增加系統數據回收的可靠性,本文介紹了基于雙備份存儲的數據采集存儲系統的設計與實現方法。

本文引用地址:http://www.j9360.com/article/189646.htm1 技術要求

在某飛行體遙測系統中,為了獲取飛行體的參數,需要設計一種數據采集存儲系統,要求實現對23路模擬信號的采集、編幀存儲。要求輸入信號電平為0~5 V,系統總采樣率為245.76 kHz, 記錄時間不小于500 s,對速變信號的采樣率為5.12 kHz,緩變信號的采樣率為160 Hz, 23路模擬量信號輸入中包括9路速變信號和14路緩變信號。

2 整體方案的設計

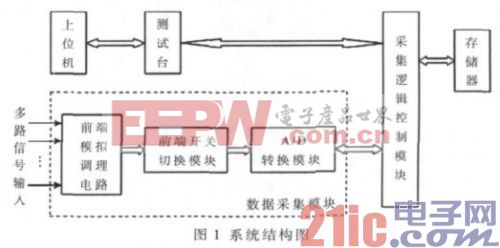

信號采集存儲系統是基于雙備份的數據存儲器設計而成,整個系統以FPGA為核心控制器,控制數據的采集、編幀存儲。系統結構如圖1所示。

2.1采編器電路的設計

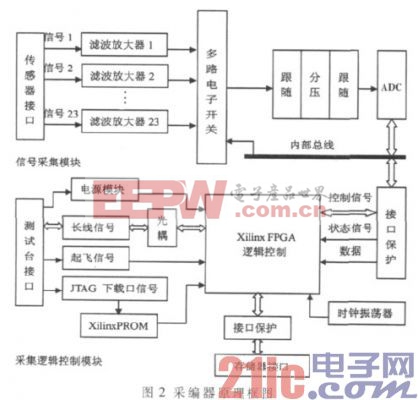

采編器[2]主要完成對各種被測信號的采集,并對數據進行實時編碼、邏輯控制和實時存儲控制,分為速變、緩變信號采集模塊和采集控制模塊,兩者通過內部總線相連。

速變、緩變信號采集模塊主要完成23路輸入模擬信號的調理、選擇、A/D采集等功能,包括輸入接口電路、濾波跟隨電路、模擬通道切換電路、信號調理電路等。

采集控制模塊完成模擬信號的A/D采集控制、編幀、內部時序控制等功能,包括長線接口電路、控制電路、存儲器接口電路、幀結構下載電路等。

采編器的主控器件采用XC2S100E型現場可編程門陣列(FPGA),該器件體積小、功耗低、內部延時小,全部控制邏輯由硬件自動完成,編程配置靈活,可實現程序的并行執行,因而可大大提高系統的工作性能。該采編器的電壓采集范圍為0~+5 V,采集精度不低于0.1%。由于FPGA本身不具備A/D轉換模塊,因此各通道的模擬信號分別經信號調理電路后,由模擬多路開關ADG506選擇模擬通道,再經外部高速AD7667實現A/D轉換,轉換的數據在FPGA內編幀后輸出到存儲器中。具體的每幀數據由各路模擬信號和幀標記FDB1 8540組成。采編器的電源由電源模塊提供的5 V電壓經TPS70351調理后產生。

采編器電路框圖如圖2所示。

2.2存儲器電路的設計

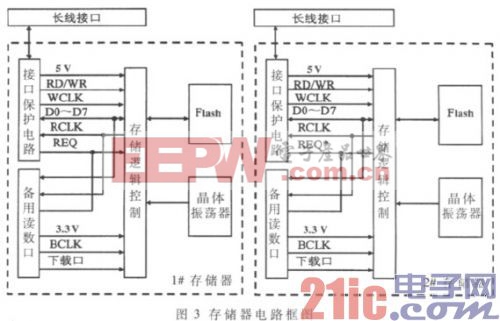

存儲器主要完成數據的存儲功能,存儲器包括兩套獨立的存儲電路A、B片,兩者互為備份。每套存儲器內包括與采編器相連的長線接口、FPGA和Flash存儲芯片。該雙備份設計能進一步提高數據回收的可靠性。

存儲器電路框圖如圖3所示。

技術要求總采樣率約250 kHz,記錄時間不小于500 s, A/D采集的有效位數為16 bit,則一個采樣周期(即4 μs)產生的數據量為2 B, 則1 s的數據量為1×106×2/4=500 000 B,則500 s內的記錄數據量為2.5×108 B=238.5 MB, 可見容量為256 MB的閃存芯片便可滿足記錄要求,本設計采用SAMSANG公司的Flash存儲芯片K9K8G08U0M,存儲容量達1 GB,是為了留出存儲余量,這樣就為以后系統的升級和擴展提供可行性解決方案。

評論