基于FPGA的車道偏離預警系統的設計

2.1 SOPC系統的設計

SOPC系統的核心為Nios II CPU,本文選用的是標準型Nios II IP核,用以在硬件規模和性能之間取得平衡;JTAG UART用以完成FPGA配置及系統調試;顯示接口IP包括SDRAM、SRAM、FLASH的IP核完成SOPC系統與FPGA外部存儲器件的連接與通信;人機界面器件接口完成LED、LCD、按鍵與SOPC系統的連接。

2.2 圖像信號處理單元的設計

圖像信號處理單元利用Verilog HDL實現了基于FPGA的圖像預處理、中值濾波及Sobel邊緣檢測功能,設計過程中,充分利用TFPGA適于并行處理和流水處理的特性。

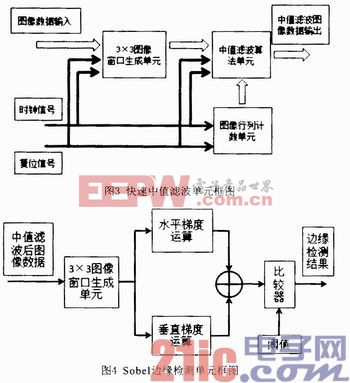

2.2.1 快速中值濾波單元

快速中值濾波單元主要由3×3模板生成模塊、中值濾波算法模塊及行列計數模塊組成,其單元框圖如圖3所示。本文引用地址:http://www.j9360.com/article/189559.htm

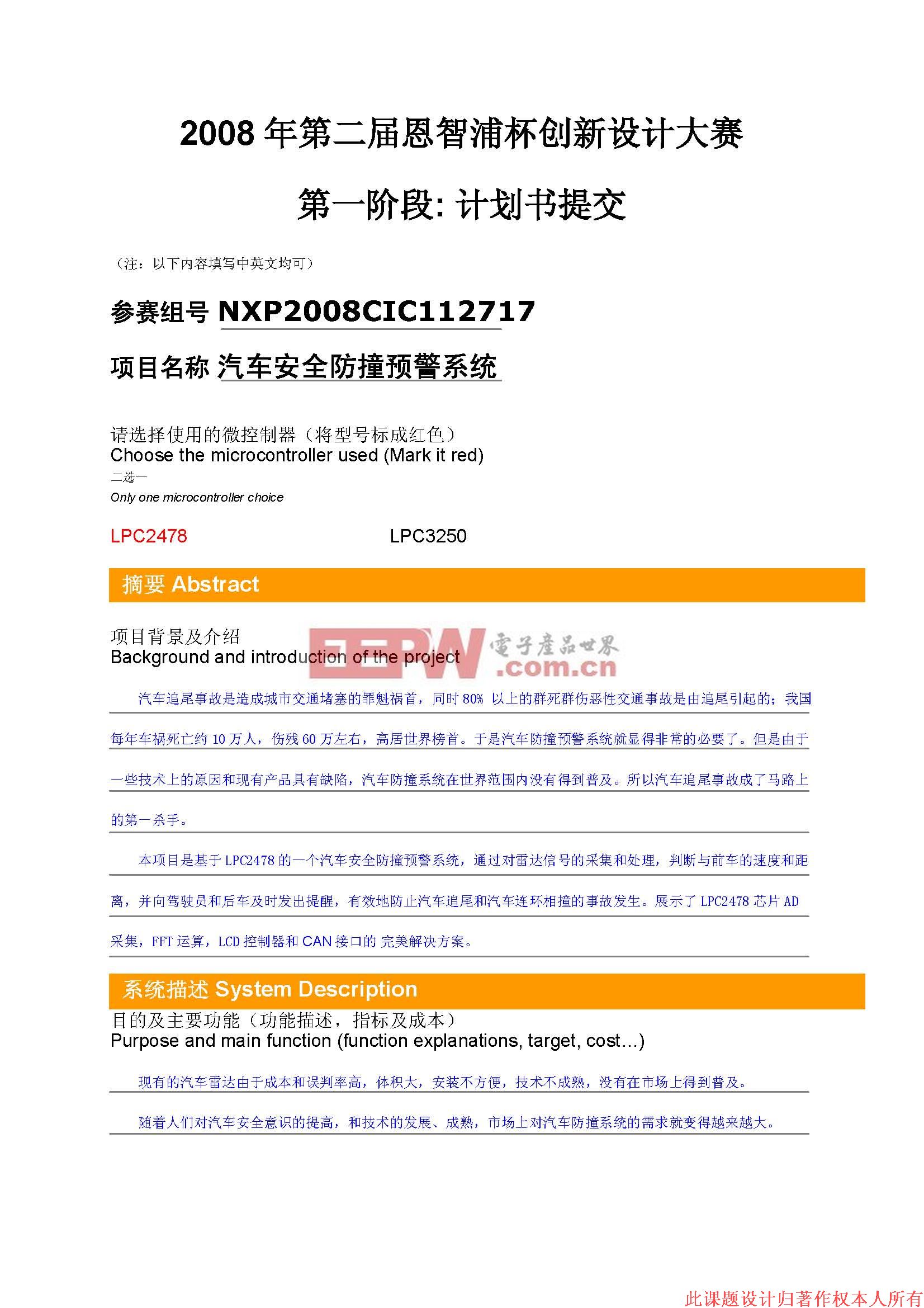

2.2.2 Sobel邊緣檢測單元

Sobel邊緣檢測單元由3×3模板生成模塊、梯度運算模塊、梯度比較輸出模塊三部分組成,其單元框圖如圖4所示。三部分按照流水線的方式工作,通過窗口模板的移動,完成整幅圖像的邊緣檢測任務。

fpga相關文章:fpga是什么

評論