DM642開發與應用

視頻實時處理,由于視頻處理中數據量大,要求速度快因此采用TM320DM642。視頻處理機應用于視頻采集、視頻處理、視頻輸出的視頻實時處理。視頻處理機的解決方案有多種選擇,但是市場主流產品一般選擇兩種方案:1)采用CPU+ASIC。2)采用雙CPU結構,即一個嵌入式CPU和一個專用信號處理芯片DSP。受專用DSP芯片處理能力的限制,現有的嵌入式中使視頻處理機的視頻處理算法基本是H.263以下的標準。

l 硬件設計

本文介紹一種基于TMS320DM642 DSP的視頻采集設計方案。其操作系統、通信協議、網絡協議、音視頻處理軟件均在一顆TMS320DM642上實現,降低了開發的難度。

TMS320DM642芯片簡介:

TI公司的TMS320DM642(以下簡稱DM642)是一款專門面向多媒體應用的專用DSP。該DSP時鐘高達600MHz,8個并行運算單元,處理能力達4800MIPS;采用二級緩存結構;具有64位外接存儲器接口;兼容IEEE―1149.1(JTAG)邊界掃描;為了面向多媒體應用,還集成了3個可配置的視頻端口、面向音頻應用的McASP(Multi Channel AudioSerial Pott)、10/100Mb/s的以太網MAC等外設。鑒于DM642的上述優點,本網系視頻處理機統以DM642為核心,完成音視頻信號的實時采集、壓縮及傳輸功能。

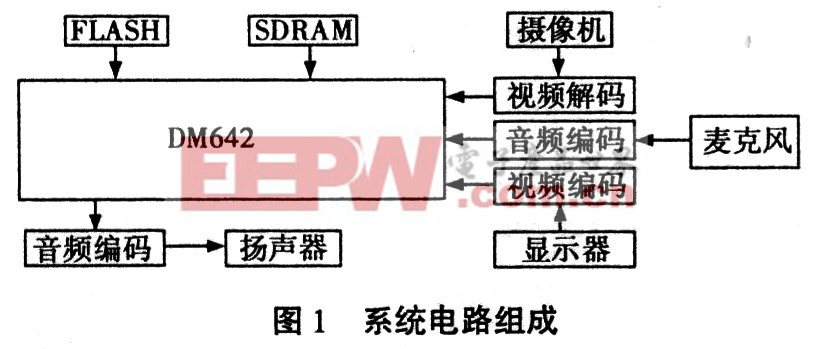

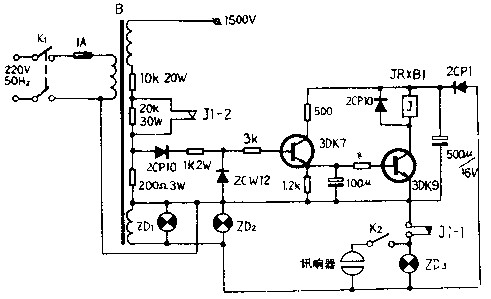

系統電路組成如圖1所示。從視頻處理機的視頻信號和從麥克風輸入的音頻信號經采集、A/D轉換為數字信號后送入DSP。DSP在信源處對音視頻信號進行壓縮編碼和合流,然后通過局域網或因特網將數據傳輸給視頻監控中心。監控中心可同時監視多個現場,接收或發送報警信號,并根據需要通過異步串行總線RS-485實時控制,調整攝像頭的方向和位置。

1.1 視頻采集電路

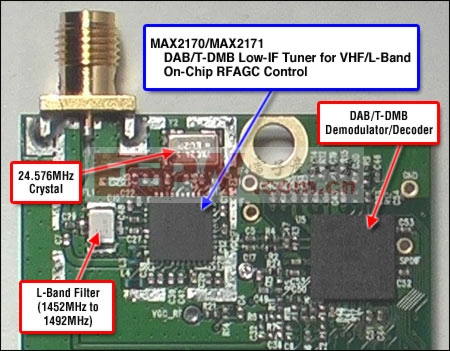

本系統采用的視頻解碼芯片是Philips公司的SAA7115。從模擬視頻輸入口輸入的全電視信號在SAA7115內部經過鉗位、抗混疊濾波、A/D轉換、YUV分離電路之后,在YUV到YCrCb的轉換電路中轉換成BT.656視頻數據流,輸入到壓縮核心單元DM642中。DM642的3個視頻口VP0、VP1、VP2與視頻編解碼芯片相接。在本系統中,只有一路視頻輸入,故VP1、VP2端口,VP0通道配置為8位BT.656視頻輸入口。視頻數據的行/場同步信號包含在BT.656數字視頻數據流的EAV(end ofactive video)和SAV(start of active video)時基信號中,視頻口只需視頻采樣時鐘和采樣使能信號即可。SAA7115內部寄存器參數的配置和狀態的讀出通過I2C總線進行。視頻接口的原理如圖2所示。

1.2 視頻編碼電路

本系統采用的視頻編碼芯片是Philips公司的SAA7105H。DM642的視頻口2用來驅動視頻編碼器,視頻信號經過FPGA芯片,連到視頻編碼芯片PhilipsSAA7105H。FPGA用于擴展屏幕顯示功能。視頻輸出信號支持RGB,高清晰度視頻,PAL/NTSC復合視頻和s端子視頻信號。通過DM642的I2C總線對的內部寄存器編程實現不同輸出。

1.3 音頻輸入/輸出電路

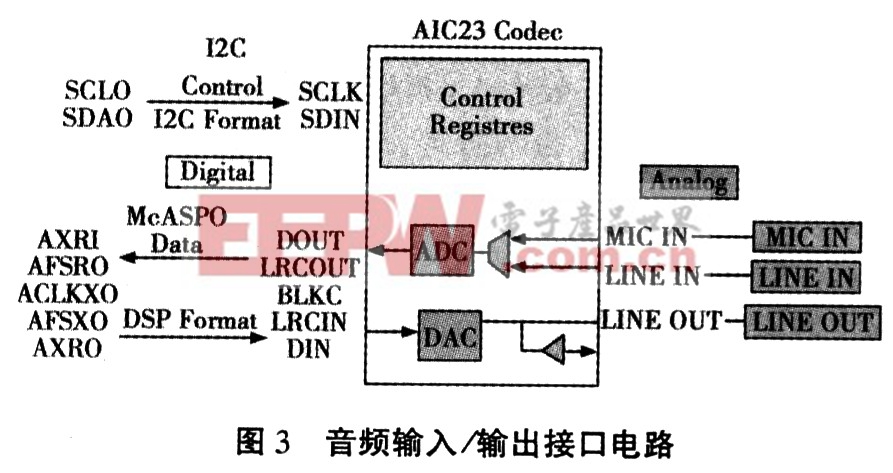

本系統采用TI的高性能立體聲編解碼器TLV320AIC23(以下簡稱AIC23)實現音頻信號的采集和播放。AIC23與DM642的I/0電壓兼容,可以實現與DM642的McASP接口無縫連接。在本系統中,AIC23工作于主模式,左右聲道的采樣字寬均為16bit。數據接口為DSP mode模式。通過I2C總線設置內部寄存器的工作參數和反饋狀態信息。

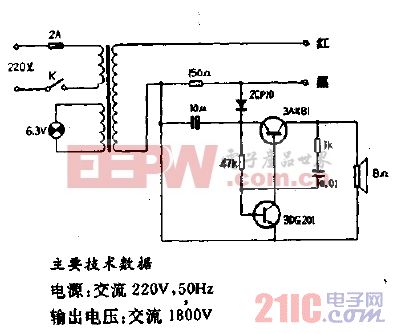

因為網絡傳輸的固有特點,音頻數據和視頻數據從網絡攝像機端到達監控中心不可能是均勻的,如果網絡攝像機端不做任何糾正處理,則很難保證音視頻的同步輸出。為了實現音頻和視頻的采樣同步,本文利用鎖相環PLLl708,從SAA7115的LLC引腳輸出27MHz時鐘,經PLLl708產生AIC23的主時鐘MCLK。由于音視頻采樣信號采用同一個時鐘源,就不會出現音視頻不同步的問題。PLLl708的SCKO3引腳輸出默認時鐘頻率18.433MHz,作為AIC23的輸入主時鐘MCLK。AIC23內部采用的時鐘可通過設置寄存器由主時鐘MCLK分頻得到如圖3。

評論