基于FPGA和USB2.0的高速數據采集系統

本文引用地址:http://www.j9360.com/article/188574.htm

2 硬件設計

系統的硬件由A/D轉換電路、數據采集與傳輸控制電路和接口電路構成。

2.1 A/D轉換電路

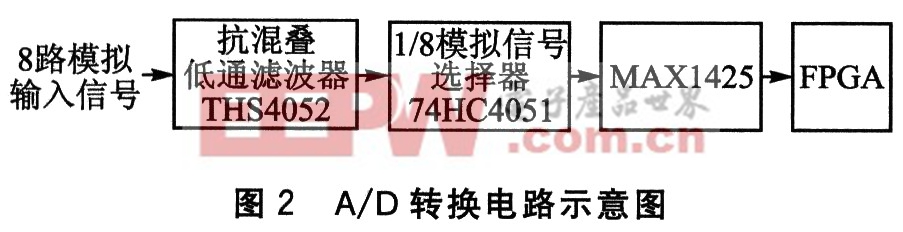

A/D轉換電路是整個系統的重要組成部分。由低通濾波器、多路選擇開關和A/D轉換器構成,如圖2所示。本文選用Maxim公司的A/D轉換芯片MAX1425。

8路模擬輸入信號分別經過由運放THS4052構成的抗混疊低通濾波器去除高頻成分,防止信號產生“混疊現象”。1/8模擬信號選擇器根據來自FPGA板的地址碼,控制模擬信號選擇器74HC4051選通8路輸入中的1路到輸出端,送到A/D轉換器MAX1425將模擬信號轉換為數字信號。MAX1425的控制信號由FPGA板提供,在控制信號的作用下以適當的時序完成轉換工作。

2.2 數據采集與傳輸控制電路

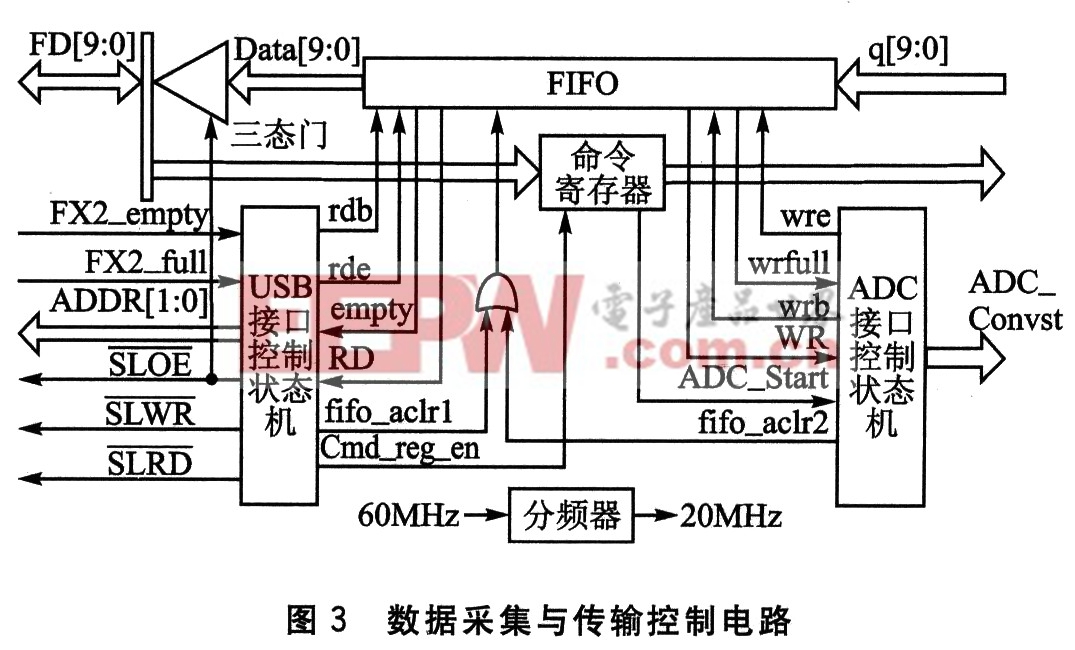

數據采集與傳輸控制電路的開發工作主要集中在FPGA上。FPGA負責CY7C68013與ADC芯片之間的緩沖與控制,一邊與ADC接口,另一邊與USB接口,產生數據采集、通道切換、A/D轉換、FIFO所需的全部控制信號;實現對傳輸數據的緩存、讀/寫控制、時鐘、輸出使能、端點的選擇,以及對ADC的控制等功能。

如圖3所示,數據采集與傳輸控制電路由FIFO、USB接口控制狀態機、ADC接口控制狀態機、三態門緩沖器、控制寄存器組幾部分構成。圖中,由右向左的寬箭頭表示數據流;FD[9:0]是與USB接口芯片連接的雙向數據總線;由左向右的寬箭頭表示傳送來自PC機的控制信號;單線箭頭表示輸入/輸出,以及FPGA內部各個模塊間的控制信號線。

從數據流向看,數據在ADC接口控制狀態機的協調下通過ADC接口送入FPGA的FIFO中。經過FIFO的緩沖后,在USB接口控制狀態機的協調下,當USB接口控制狀態機對三態門的輸出為高時,三態門開啟,數據通過三態門傳輸到FPGA外部的USB接口;當對三態門的輸出為低時,三態門呈現高阻態,FPGA的這幾個引腳作為輸入引腳。此狀態下,來自PC機的控制信號通過CY7C68013從FD[15:0]送人FPGA中。在USB接口控制狀態機的控制下,來自PC機的控制信息存人控制寄存器組,并由ADC接口控制狀態機來控制送往FPGA外的ADC接口,作為對ADC的控制(如通道的選擇)。

評論