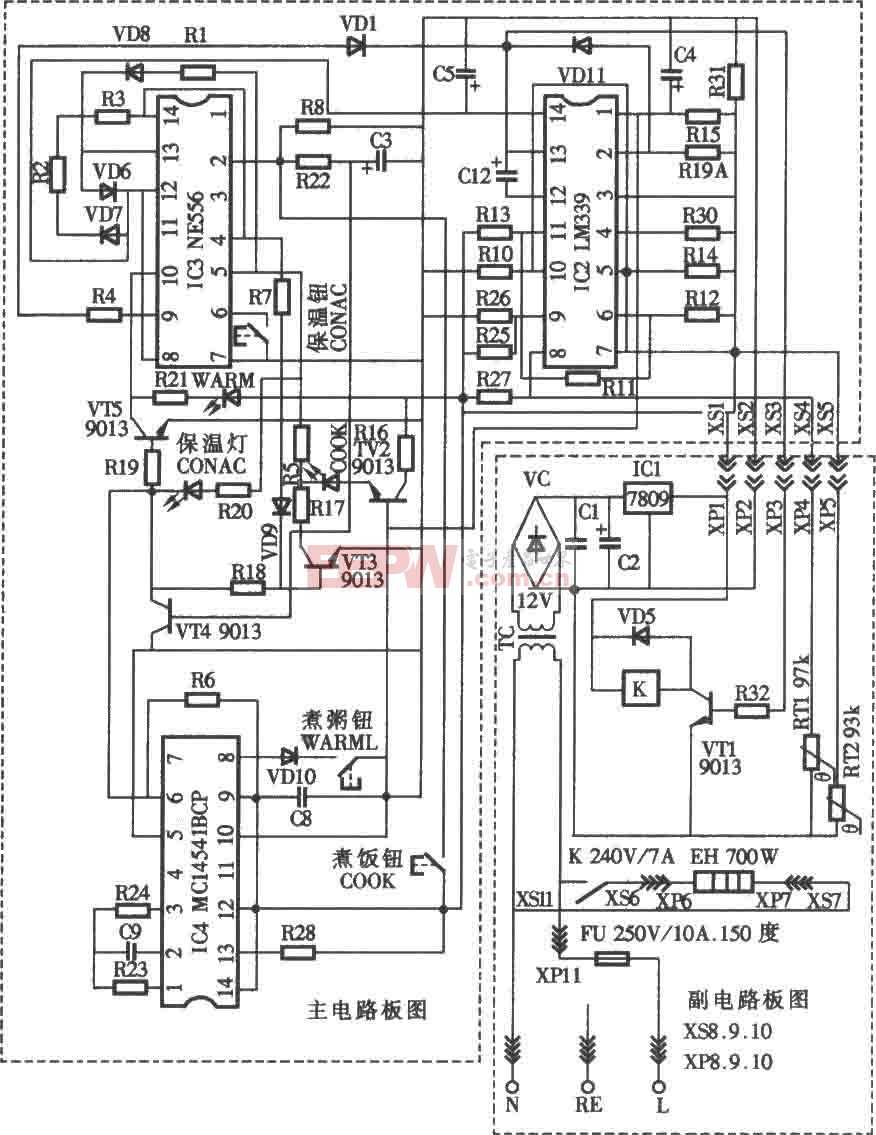

STM32F1 0x在應用中編程的實現方法

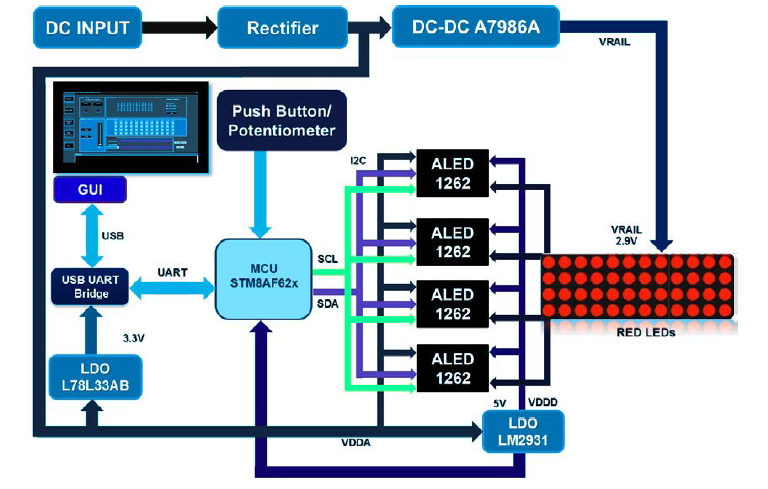

Cortex-M3是首款基于ARMv7-M體系結構的32位標準處理器,RISC結構,包含高效靈活的Thumb-2指令集,擁有杰出的低功耗特性,為微控制器系統、汽車車身控制系統、工業控制系統和無線網絡等嵌入式應用量身設計。ST公司推出基于Cortex-M3內核的STM32系列處理器,憑借其出眾的性能、創新的外設、優越的功耗控制,得到眾多工程師的青睞。

針對嵌入式應用的特點,STM32處理器提供功能強大的硬件調試接口――JTAG接口和串行接口,極大方便了設計,縮短了產品的開發周期。不僅如此,STM32處理器內嵌的閃存存儲器允許在電路編程(In-Circuit Pro-gramming,ICP)和在應用中編程(In-Application Program-ming,IAP)。利用在應用中編程,僅需通過一根串口線,就可以完成產品固件的更新。本文對STM32處理器的在應用中編程進行了詳細的分析,結合硬件和驅動給出了IAP的具體實現方法,稍加修改,便可應用于STM32處理器的所有系列產品。

1 STM32F10x處理器

1.1 STM32處理器特點

STM32全系列處理器具有腳對腳、外設及軟件的高度兼容性。這給應用帶來很好的靈活性,易于將應用升級到不同存儲空間或不同封裝的平臺。STM32處理器的產品全系列兼容,使得項目之間的代碼重用和移植很方便。

1.2 STM32處理器內存映射

Cortex-M3的存儲系統采用統一編址的方式,程序存儲器、數據存儲器、寄存器被組織在4 GB的線性地址空間內,以小端格式(little-endian)存放。內存映射如圖1所示。

在代碼區,0x00000000地址為啟動區。上電以后,CPU從這個地址開始執行代碼0x08000000為用戶Flash的起始地址,0x1FFFF000為系統存儲器(system memory)的起始地址。對于STM32處理器,可以通過配置BOOT0和BOOT1兩個引腳來選擇不同的啟動模式,如表1所列。CPU在時鐘信號的第4個上升沿鎖存BOOT引腳的值,根據兩個引腳的值將對應的存儲器物理地址映射到啟動區。

系統存儲器也稱為“大信息塊”,有2 KB的容量。所有上市的STM32處理器,在出廠前已經燒寫進去自舉模式下的啟動程序(Bootloader),并且將之鎖定防止用戶擦寫。通過配置BOOT0和BOOT1選擇系統存儲器啟動,相應的啟動程序在復位后得以執行,配合PC端的通信軟件,通過USART1口允許用戶將程序燒寫到用戶Flash區。之后,將BOOT0和B00T1重新配置為用戶Flash存儲器啟動,進入正常的應用程序。

上述的自舉模式類似于ISP編程,相比其他燒寫方式方便許多,但真正方便靈活的是在應用中編程(IAP),只需一根串口線就可以載入程序,復位后立即執行新的應用程序。

2 IAP功能原理

在應用中編程(IAP)使得用戶可以在程序運行時重新對Flash進行編程。簡單地說,IAP的編程工作是:下載編譯好的二進制文件數據到RAM;將數據重新編程到特定的Flash區。這兩個工作是由IAP驅動程序完成的。使用IAP功能后,系統的固件由2部分組成:第1部分是IAP驅動,不執行通常的功能,而是通過微控制器支持的任一種通信管道(如USB、USART、SPI等,本文使用USART)接收數據,并執行對第2部分代碼的更新;第2部分是真正的應用程序代碼,實現具體的功能。這兩部分代碼共同燒寫在Flash中。要注意的是,這兩部分代碼不能重疊,否則無法實現IAP功能。

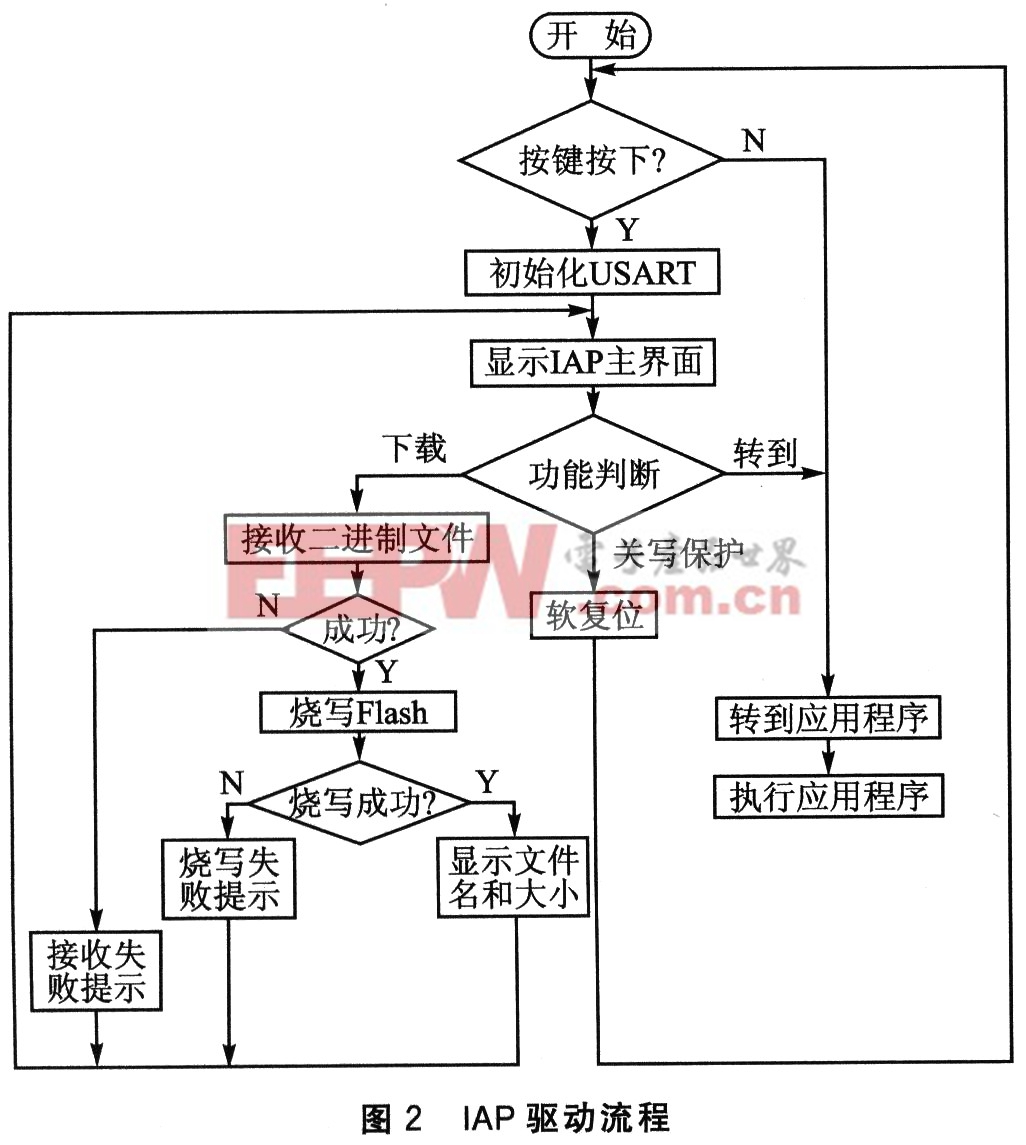

系統上電以后,IAP驅動首先運行,它主要執行如下的操作:

①根據硬件信號或軟件條件判斷是否需要對第2部分代碼進行更新;

②如果不需要更新,則跳轉到④;

③執行更新操作;

④跳轉到第2部分代碼執行。

STM3210x處理器IAP驅動的流程如圖2所示。圖中顯示IAP主界面是利用超級終端實現的,傳輸協議用的是Ymodem協議。需要注意的是,由于IAP驅動占用了用戶Flash區的一段起始空間,因此Flash的可編程最大空間要把這部分除去。

3 IAP功能實現

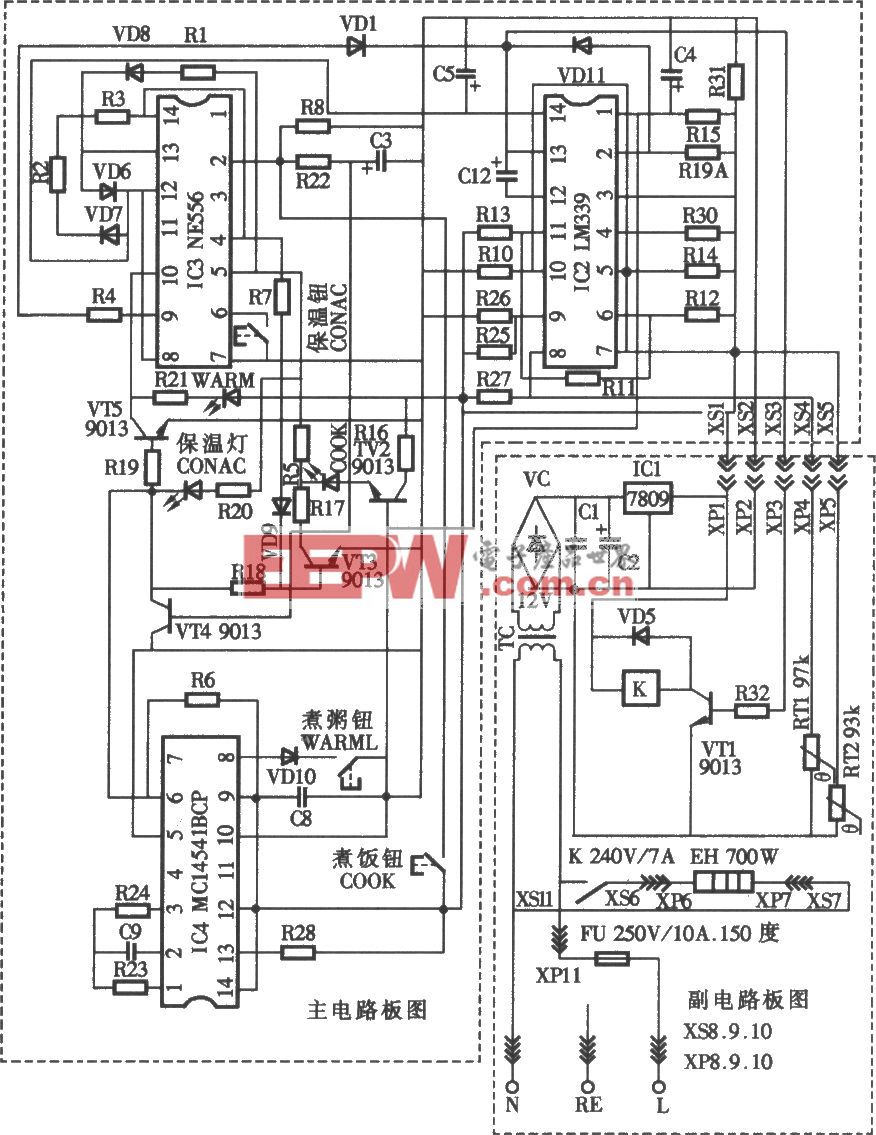

3.1 硬件電路

采用STM32F10x型處理器作為核心。該處理器可全速工作在72 MHz,擁有3個USART接口,內嵌128 KB Flash和20 KB SRAM。Flash是以頁的形式組織的,擦除1頁的時間約為20~40 ms;在整個工作范圍內其擦除次數可達10 000次,經10 000次擦除后,在+55℃的保存環境中數據保存期限仍可達20年。用戶完全不必擔心使用了IAP功能后對產品造成不良影響。

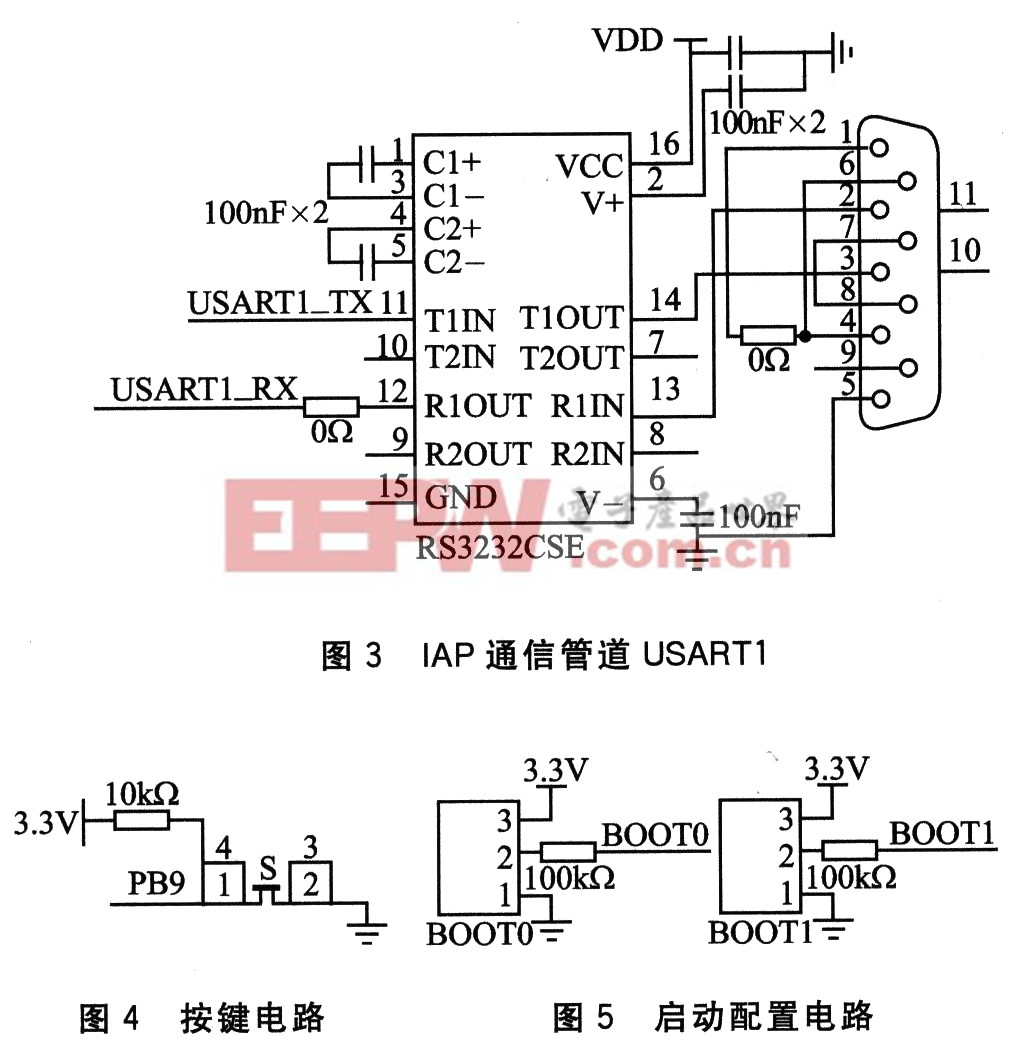

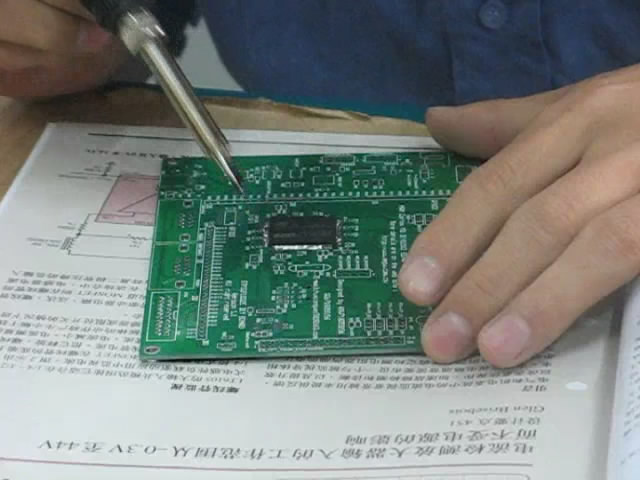

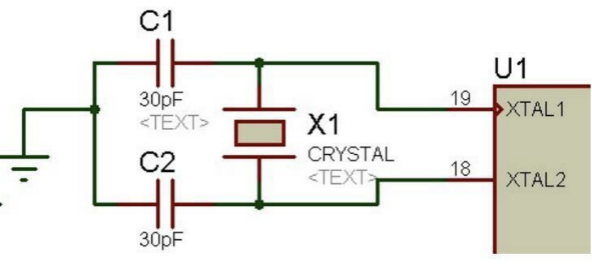

IAP驅動使用USART1口作為通信管道,PB口的第9引腳作為IAP判斷是否進入IAP功能的信號線。引出一個按鍵,作為IAP功能選擇按鍵,只要在上電或復位時按住此鍵就會進入IAP功能主界面,否則直接執行正常應用程序。BOOT0和BOOT1是啟動配置跳線。相應的硬件電路分別如圖3、圖4和圖5所示。

存儲器相關文章:存儲器原理

評論