基于NCO IP core的Chirp函數實現設計

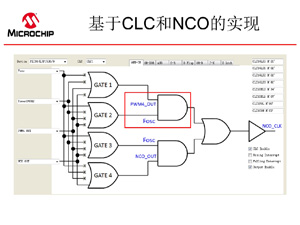

IP就是知識產權核或者知識產權模塊的意思。在EDA技術和開發領域具有十分重要的作用,在半導體產業中IP定義為用于ASIC或FPGA/CPLD中預先設計好的電路功能模塊。IP可以分為軟IP,固IP和硬IP三種。

隨著電子系統的越來越復雜,PLD設計的越來越龐大,這就增加了市場對IP核的需求,各大FPGA/CPLD廠商陸續推出了許多IP核。例如:FIR(有限沖擊響應)數字濾波器core;FFT(快速傅里葉變換)core,NCO(數控振蕩器)core等,在設計中如果使用了這些知識產權核可以大大簡化FPGA/CPLD的設計,加速設計速度,縮短研發周期,并且較之于開發者自己的設計程序,這些IP有更好的運算精度、速度、SFDR參數、SNR參數等,達到良好的效果!

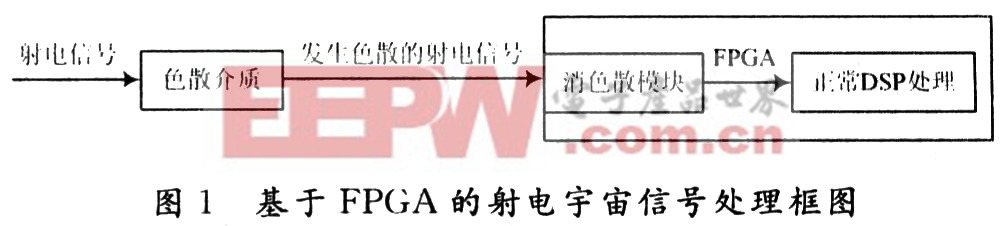

由于電磁波在傳輸過程中,經過色散介質,如不均勻的波導經過高空電離層時會發生色散現象。Chirp函數在射電天文信號的消色散處理中發揮著重要的作用,研究在FPGA中實現Chirp函數是基于FPGA的射電宇宙信號處理的重要組成部分。如圖1所示。

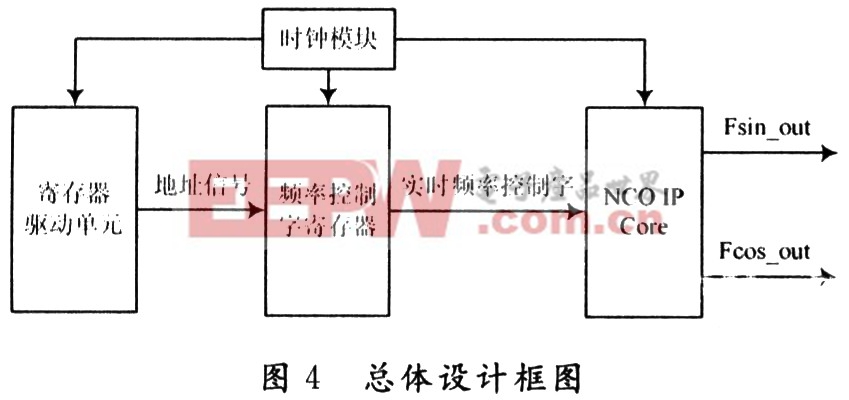

該設計就是通過實時的改變NCO IP core的輸入頻率控制字的辦法,數控頻率輸出的辦法實現Chirp函數。

1 系統總體設計

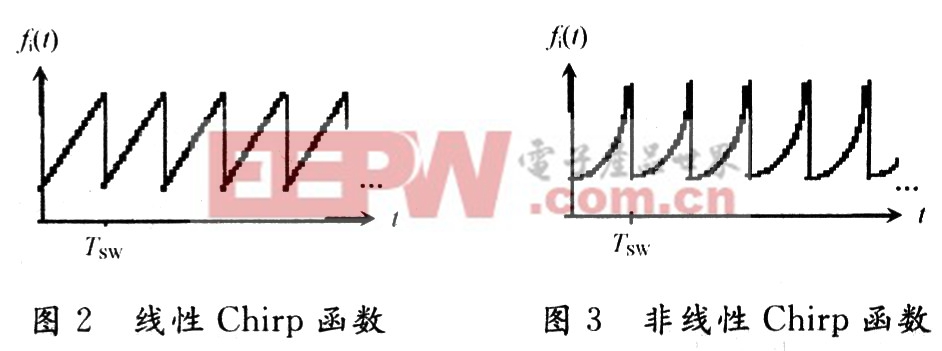

Chirp函數根據輸出頻率的遞變規律一般分為兩種:線性Chirp函數和非線性Chirp函數,以下是兩種Chirp函數在頻域上的表現如圖2,圖3所示。

從圖2,圖3可以看出Chirp函數的頻率輸出與時間的f-t關系可以總結為:

對于線性Chirp函數:

在連續域時間域內有關系式:

![]()

式中:k為常數;f0為初始輸出頻率;t為連續時間。

在離散時間域有關系式:

![]()

式中:k為常數;f0為初始輸出頻率;n為采樣點。

對于非線性Chirp函數:在連續域時間域內有關系式:

![]()

式中:f(t)為非線性函數;f0為初始輸出頻率;t為連續時間。

在離散時間域有關系式:

![]()

式中:f(n)為非線性函數f0為初始輸出頻率;n為采樣點。由上式可以看出Chirp函數在每一個時刻點具有不同的頻率輸出,而根據具體的頻率變化的需要在每一個時刻點實時的改變其頻率控制字是實現Chirp函數的關鍵。其算法框圖如圖4所示。

評論