實現語音壓縮算法的高速硬件平臺

1 基本概念介紹

1.1 CY7C68013性能特點

CY7C68013(EZ-USB FX2)是Cypress半導體公司的新一代高速USB系列,可以用USB2.0最大數據傳輸率傳輸數據。該芯片基于EZ-USB FX芯片開發,集成有發送器、SIE、8051微控制器、存儲器和可編程IO接口,是一種完全集成的USB2.0方案[2]。

1.2 G.723.1簡介

G.723.1是一種低碼率語音壓縮標準,是H.324標準系列的一部分,也是VoIP的常用解決方案之一,可在低比特率通信終端(PSTN和無線網絡)上進行多媒體通信。使用G.723.1標準能夠將8 kHz采樣l6 bit的線性PCM語音信號壓縮成6.3 Kb/s或5.3 Kb/s的比特流,其壓縮比例較高,占用帶寬較低,而且具有很好的音質。

2 硬件設計

2.1 TMS320C6713外設接口HPI

TMS320C6713是一款高性能的32位浮點DSP,適用于專業音頻信號處理。HPI即主機接口,是TMS320C6713片上集成的外設接口之一。通過HPI 可以方便地實現多處理器系統,外部處理器作為主處理器,DSP作為從處理器。通過HPI 接口,外部主機可以訪問DSP除L2控制寄存器、中斷選擇寄存器、仿真邏輯之外的全部存儲器映射空間。

2.2 讀寫時序

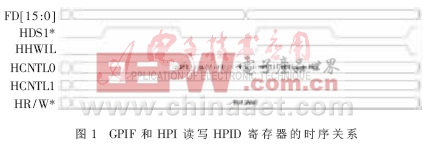

本實驗采用CY7C68013和TMS320C6713芯片。在GPIF接口部分,IFCLK設置為48 MHz內部時鐘,使用16位寬的數據總線(設置WORDWIDE=1),分配CTL[2:0]控制HPI的時序。使用GPIF Tool生成波形描述符,分別用于HPIC/HPIA/HPID的讀寫控制。值得注意的是:由于HDS1*/HDS2*/HCS*相關,可以使HCS*有效,HDS2*置“1”,并通過HDS1*控制選通;HHWIL控制傳輸的是第一半字還是第二半字;HCNTL[1:0]決定哪個寄存器正被訪問[3]。由于采用DIN連接器,其傳輸速率最高可達幾十兆赫茲,這也是其傳輸瓶頸。如果采用手工單獨裝配的SMA硬件連接器,其硬件連接的速度完全可以滿足GPIF和HPI的要求。當然,前者每個引腳的成本不到后者的百分之一[1]。圖1為GPIF和HPI讀寫HPID寄存器的時序關系圖。

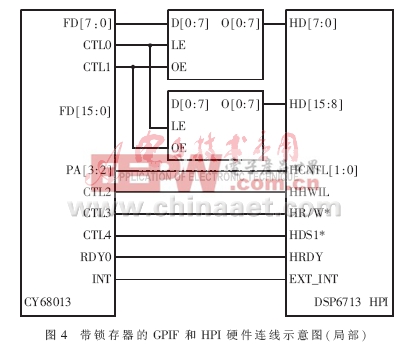

通過FX2固件、利用非GPIF I/O信號引腳可實現更多的信號輸出。使用DM74LS573N鎖存器,采用數據鎖存的辦法可以減小由布局布線等原因帶來的互感、串聯電感、寄生電容等減緩信號傳播的影響,在硬件測試階段能夠有效解決傳輸誤碼的問題。由于74LS573的傳輸延遲,系統的可靠性建立在犧牲系統帶寬的基礎上。改用74LVC16245雙向緩沖器,可以實現GPIF主控的數據讀、寫功能。圖2為帶鎖存器的GPIF和HPI讀寫HPID寄存器的時序關系圖。

2.3 硬件連線

系統整體硬件連線示意圖如圖3。

圖4為帶鎖存器的GPIF和HPI硬件連線示意圖。

3 軟件設計

此方案包括4個方面的程序設計:固件程序、驅動程序、主機應用程序和DSP數據處理程序。

3.1 固件程序

固件程序是指運行在CY7C68013 51內核中的程序,主要包括設備描述符信息、設備功能代碼和USB同DSP處理器間的通信控制功能代碼。對于使用GPIF的FX2系統,固件還應能夠分配FIFO讀和寫波形到4個FIFO中的任何一個。

3.1.1 固件程序設計

固件程序開發基于KEIL C51,使用Cypress公司提供的固件函數庫Ezusb.lib和固件框架以提高開發效率。固件函數庫提供了一系列與USB協議有關的函數,固件框架已經實現了初始化、重枚舉、電源管理等功能。

評論