具有PCI和并行接口的數據采集系統設計

1 引言

本文引用地址:http://www.j9360.com/article/188333.htm隨著計算機技術的飛速發展和普及,數據采集系統也迅速地得到應用。在生產過程中,應用這一系統可對生產現場的工藝參數進行采集、監視和記錄,為提高產品質量、降低成本提供信息和手段。典型數據采集系統的構成是由A/D+DSP+FPGA(CPLD)+D/A。本文通過利用模數轉換芯片AD6644,以及FPGA實現了可用于兩種接口(PCI、并行接口)傳輸模式下的高精度數據采集系統。

2 硬件電路設計

2.1 系統設計方案

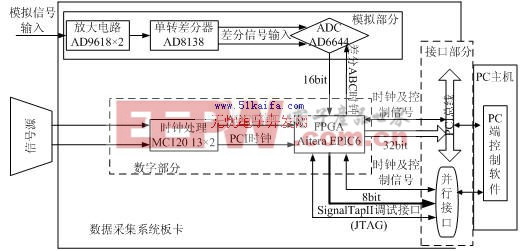

本數據采集系統主要由模擬部分,數字部分和接口部分三大板塊組成,如下圖1所示。其中模擬部分主要包含模擬中頻信號預處理模塊和模數轉換模塊;數字部分除時鐘產生電路外,其余部分完全在FPGA中設計完成;接口部分包含PCI總線接口、DB25并行接口以及SignalTapII邏輯分析儀調試接口。

本系統的設計思路就是:首先通過模擬中頻信號預處理模塊,將調整后的模擬信號輸入給A/D轉換器,然后經模數轉換之后將16bit數字信號(AD6644輸出14bit,再加上2個校驗位)直接輸出給FPGA進行存儲。在FPGA中設計了高速緩沖器DCFIFO和高速存儲器DPRAM以及一系列時序控制邏輯,以保證在預定容量下能夠實時的存儲由ADC發送過來的數據。同時,在FPGA中還設計了2種數據傳輸接口,從而使得系統可以在我們選擇的模式下進行數據傳輸,或通過并行接口,或通過PCI總線接口。

圖1 系統總體框圖

2.2 模擬中頻信號預處理模塊

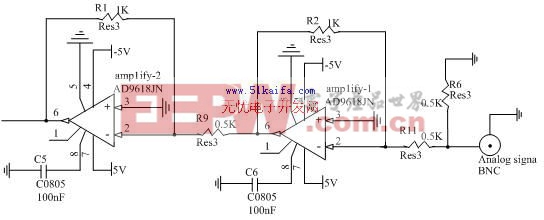

首先,將該輸入信號通過兩級放大器,目的是為了使模擬輸入信號幅度達到AD6644輸入幅度的要求和對模擬輸入信號進行很好的隔離。這里選用AD9618來實現對模擬信號的放大功能。AD9618的單位增益帶寬和壓擺率的指標均較高,能起到對模擬輸入信號放大和改善性能的作用。電路圖如圖2所示。

圖2 兩級AD9618放大器原理圖

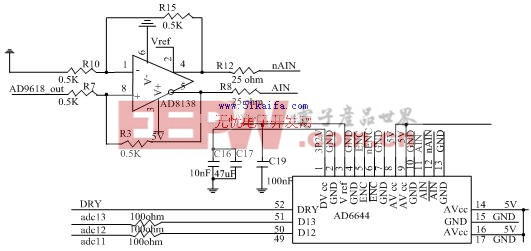

其次,將經過放大處理后的單端信號通過AD8138,轉換為差分信號后輸出給AD6644。這么做是因為作為新型的高轉換速度、大動態范圍的ADC,為保證其性能,AD6644的模擬輸入信號要求差分形式。在模擬信號階段使用差分形式,可以有效地濾除偶次諧波分量,同時對其它共模雜散信號(如由電源和地引入的噪聲)及對晶振的反饋信號也有很好的抑制作用。如下圖3,使用AD8138對模擬信號進行調整。單端模擬信號(AD9618_out)由AD8138轉換為差分模擬信號(AIN、nAIN),增益為1,然后送AD6644實現模數轉換。AD8138的直流偏壓VREF由AD6644的精密參考源提供。采用差分輸入比單端輸入大約可以提高信噪比3dB。

2.3 FPGA配置與模數轉換模塊

FPGA部分是本系統的核心模塊,承載了所有的數字電路部分。在設計過程中,強調SOC(片上系統)的概念,在FPGA平臺上實現了系統中所需要的所有數字邏輯,包括觸發器、存儲器,緩沖器,PLL(鎖相環),計數器,譯碼器,多路選擇器,DB25接口邏輯,PCI接口邏輯等。從而使得系統中的數字部分處于完全可編程可調狀態,只需根據需求更新FPGA程序即可,具有較強的適應性和靈活性。基于上述思路,我們選擇了Altera公司的Cyclone系列FPGA――EP1C6Q240C8。

圖3 AD8138+AD6644連接原理圖

在本系統中,使用了2種配置方式,即AS方式和JTAG方式。這2種配置方式可以共同使用,只需在板子上放置2套接線柱即可,下載電纜采用ByteBlaster II。首先使用JTAG方式配合Quartus II工具中自帶的在線邏輯分析儀SignalTap II對FPGA功能及時序進行調試,成功后再使用AS+EPCS4方式將程序下載到配置芯片EPCS4中,使得每次系統上電后,都能對FPGA自動加載程序。另外要注意,使用這種配置方式時,如果讓JTAG和AS模式同時開始加載,則JTAG模式會自動取得優先權進行程序加載,而AS模式則會自動終止。

評論