單芯片極窄微弱脈沖檢測系統設計

摘要:采用O.18 μm CMOS工藝設計了一款單芯片集成極窄微弱脈沖檢測系統,該芯片包括輸入匹配、放大器、脈沖展寬器、驅動及帶隙基準電壓電流產生電路。為提高檢測系統靈敏度,文章采用了多級放大器級聯以及有源電感。測試表明該芯片可以檢測1ns脈寬10mV的脈沖,輸出數字信號,可以應用于00K系統接收機,接收超過40M數據率的清晰視頻。該芯片低功耗、低成本,具有研究和實踐推廣價值。

關鍵詞:脈沖;檢測;放大器;有源電感

0 引言

隨著大規模集成電路的發展,單芯片方案由于成本低、體積小、功耗低等優點,被越來越多的電子系統所采用。

微弱脈沖信號檢測和識別在通信、醫療中都有廣泛應用,將微弱脈沖信號檢測系統單芯片化具有現實的研究意義。

1 微弱脈沖檢測系統框架設計

本系統的設計目標是用低成本CMOS工藝實現1ns、10mV脈沖信號的檢測,并輸出FPGA可處理的數字信號,用于超寬帶無線通信OOK接收通道,見圖l。

對于納秒級信號的檢測,傳統接收機方案采用需要高速時鐘的高速ADC來實現模數轉換,高速時鐘產生電路一般應用頻率綜合器方案,消耗較大面積和功耗,且同樣需要外接參考時鐘。

高速ADC使用時鐘的重要原因之一是為了利用正反饋來彌補放大器在高頻情況下的增益不足。隨著集成電路工藝的進步,器件寄生電容越來越小,0.18μm CMOS工藝截止頻率已達40GHz,通過使用有源電感,已可以在較低功耗下實現較高的高頻增益。

本系統要求單片集成,低成本、低功耗,采用多級放大器級聯的方案來提高檢測系統的分辨率,并對輸出信號通過延時電路來加大脈寬,降低后續基帶部分數字信號處理電路的壓力。

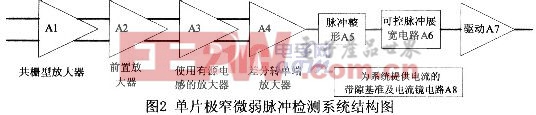

本系統具體框架見圖2所示。前一級是片外的檢波器,通過50Ω微帶線將信號輸入,所以本系統需要將輸入阻抗匹配為50Ω。本系統第一級為共柵型放大器,主要為系統實現輸入匹配,并提供一定的增益。第二級為一個4輸入放大器,可外置閾值電平。第三級為一個高頻放大

器,使用了有源電感,可以在較低功耗下達到較高的帶寬。第四級為差分轉單端放大器,將差分信號轉為單端,并提供一定的增益。第五級為一對反相器,提供非線性增益,將信號整形為數字信號。第六級為可控脈沖展寬電路,將1ns脈沖展寬為5ns。最后一級為反相器陣列組成的驅動,可以驅動5pF電容和50Ω電阻。本系統同時集成了為核心電路提供電流的帶隙基準電路。

評論