如何調整基準電壓提高ADC精度

為了提高靈活性,數據采集板應適合不同的輸入電壓范圍,利用同一采集電路處理低幅度信號時往往需要增加幾位分辨率,從而提高了系統成本。

本文引用地址:http://www.j9360.com/article/186774.htm利用本應用筆記給出的簡單電路,可以采用低成本10位ADC將實際精度提高至13位。

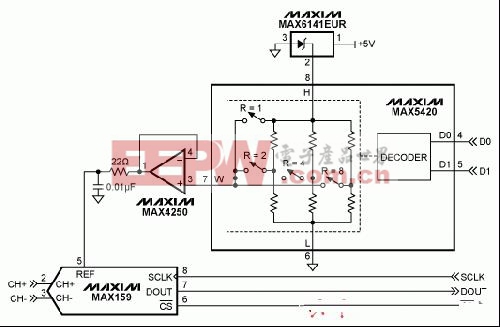

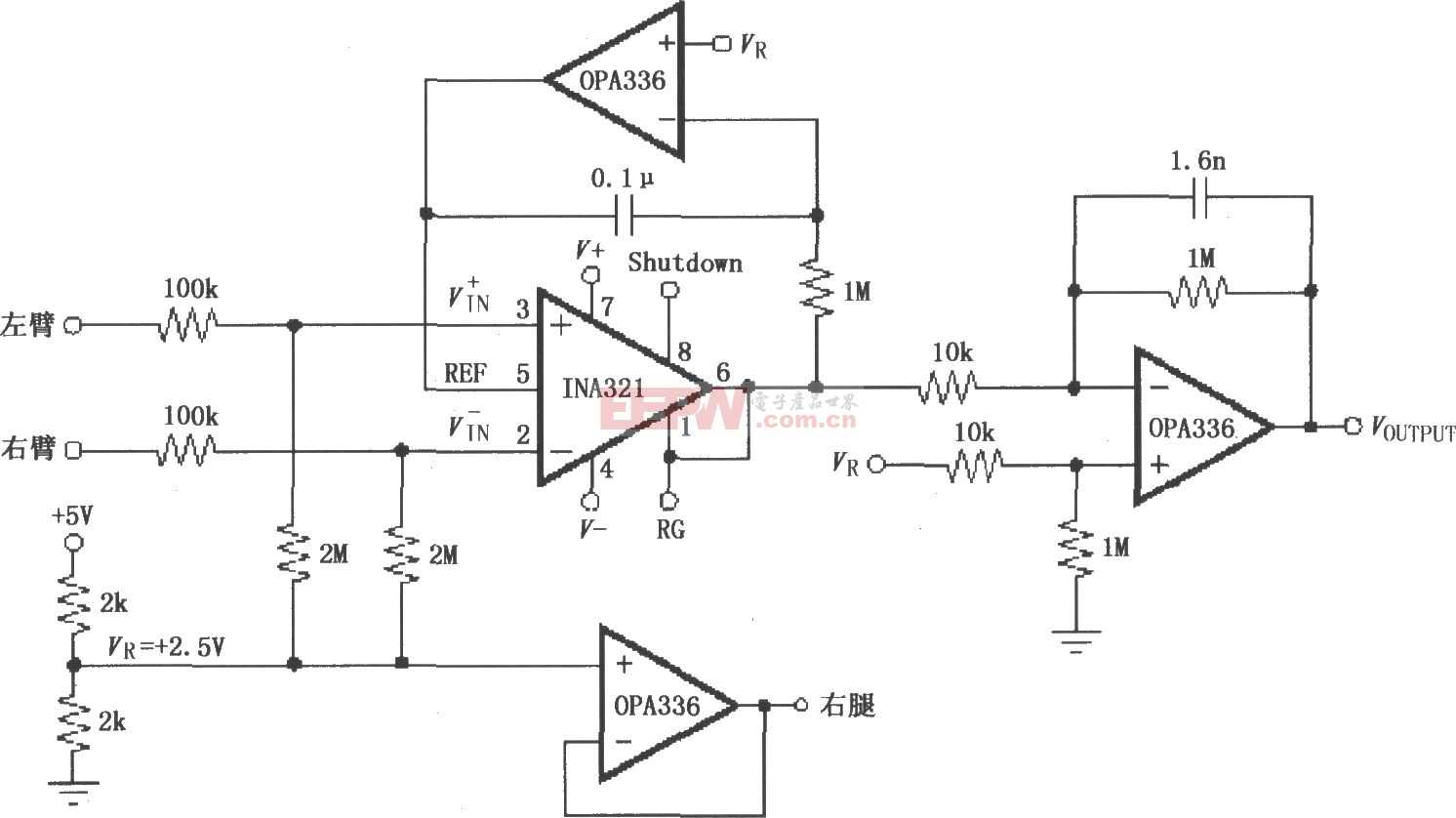

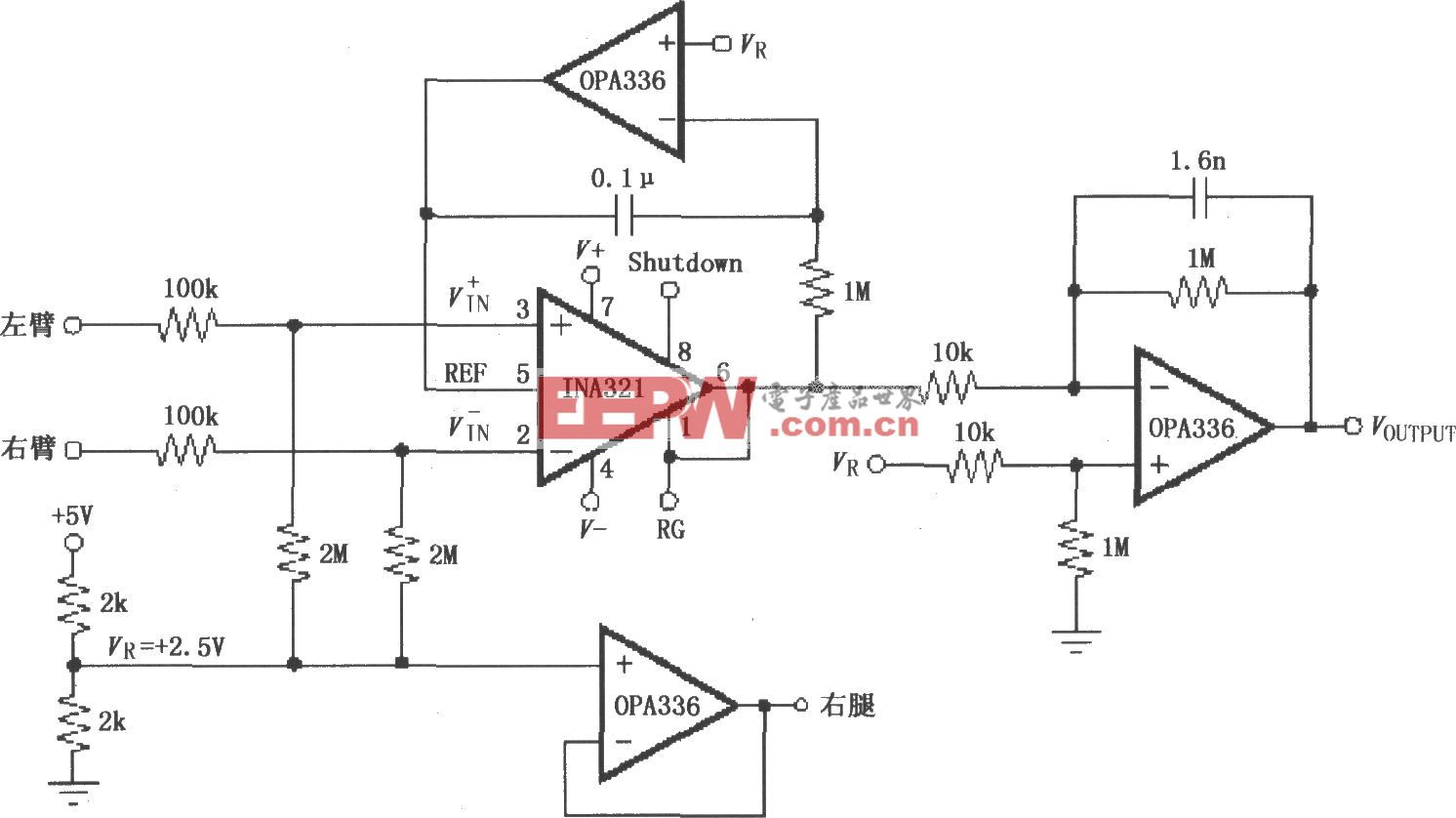

圖1

ADC的1個LSB (最低有效位)為FSR/2n,其中n表示位數。FSR (滿量程)取決于電壓基準幅度。采用外部基準的MAX159是低功耗、108ksps串行ADC,封裝于µMAX®-8,其輸入范圍為0至VDD + 50mV。較寬的輸入范圍允許利用基準縮放技術來適應不同的輸入范圍。

低成本、3端電壓基準的輸出通過數字可編程電阻分壓器(MAX5420)進行縮放調節,分壓器可提供精確的分壓比(1、2、4、8)。分壓比精度為0.025%至0.5%,取決于所選擇的器件等級(A、B、C)。分壓比由數字輸入D1和D0決定,具體如下:

表1.

DIGITAL INPUTS

D1 D0 DIVIDER RATIO

0 0 1

0 1 2

1 0 4

1 1 8

MAX6141電壓基準可提供4.096V輸出電壓。分壓比為1時,1LSB為:4.096/1024 = 4mV。不同分壓比下,1LSB對應的電壓如下表所示。

表2.

VREF (V) DIVIDER RATIO LSB (mV) VIRTUAL ACCURACY TO 4.096V FS

4.096 1 4 10-bit

2.048 2 2 11-bit

1.024 4 1 12-bit

0.512 8 0.5 13-bit

該電路中有效分辨率仍然為10位。但與4.096V FSR系統相比,實際精度得到了提高。即使在分壓比為8時,1個LSB仍然大于轉換器的典型噪底(300µV)。確保ADC性能不受限于LSB的降低。

評論