采用CSMC工藝的零延時緩沖器的PLL設計

本文引用地址:http://www.j9360.com/article/186087.htm

2.3 壓控振蕩器(VCO)

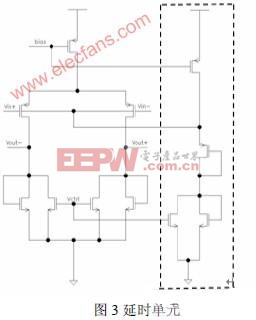

VCO 由五級差分延時單元構成的環行振蕩器。環行振蕩器對VCO 性能起著決定性的作用,它的關鍵 性能指標包括線性度、相位噪聲和抖動,因此設計從這三個方面考慮進行優化。 本文的延時單元是在傳統的差分結構上改進而來的,改進后的結構如圖3 所示。

通過改變延時單元的 控制電壓來改變每個單元的延時,調節頻率的變化,電流源的偏置電壓bias 是控制電壓Vctrl 經過偏置電 路產生的,兩者滿足一定的函數關系,它們共同變化使VCO 的輸出電壓擺幅隨頻率變化的幅度不至于過 大,同時很好的保證了頻率與控制電壓的線性關系。

延時單元選用采用差分結構是因為它有較好的噪聲抑制作用,消除了噪聲耦合中一次項分量,大大減小了電源噪聲的影響,N 阱也對P 襯底的噪聲進行了隔離;選用PMOS 差分對是考慮到PMOS 管比 NMOS 管有較小的1/f 噪聲和較小的噪聲跨導,對同樣的噪聲電壓,跨導小的PMOS 管的輸出和噪聲電 流小,引起的相位噪聲小。由其上邊的電流源偏置,對稱負載是由二極管連接的NMOS 和同樣尺寸的 NMOS 電流源并聯組成的。

分頻器相關文章:分頻器原理 電荷放大器相關文章:電荷放大器原理

評論