采用靜態(tài)CMOS和單相能量回收電路的乘法器電路設計

本文引用地址:http://www.j9360.com/article/186047.htm

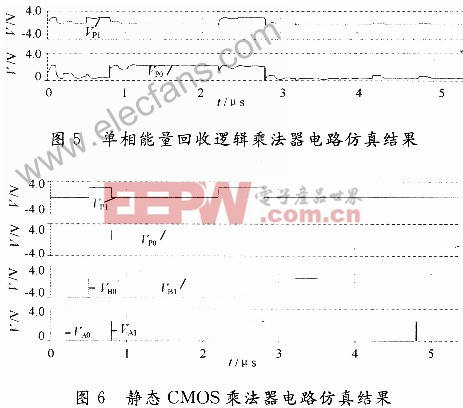

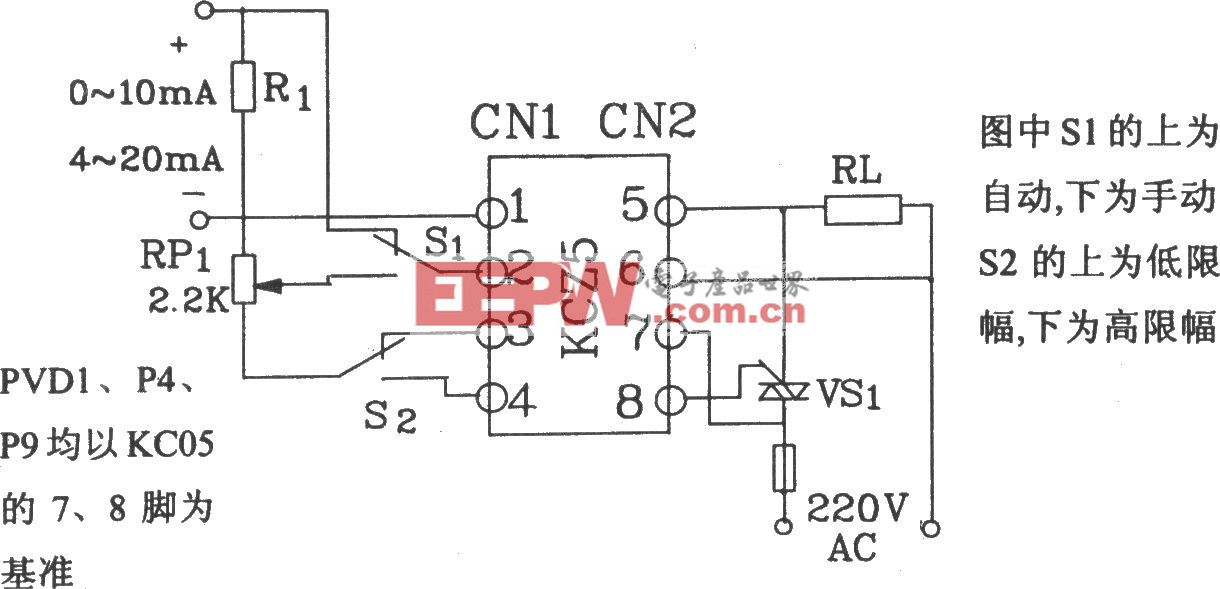

從圖中可見,用靜態(tài)CMOS電路構成的乘法器輸出比較穩(wěn)定,輸出等于0或VDD,功率消耗為1.51×10-7W。而用單相能量回收電路構成的二位乘法器的輸出不夠穩(wěn)定,對噪聲信號較為敏感,但是并不影響輸出邏輯,功率消耗減小為1.17×10-7W。從節(jié)能的角度來看,單相能量回收電路性能更好。

3 結語

本文首先介紹了單相能量回收反相器電路,詳細討論電路的工作原理,同時用PSpice工具仿真了基于靜態(tài)CMOS電路和單相能量回收電路構成的兩位乘法器電路。仿真結果表明本文介紹的單相能量回收電路能夠極大地降低電路功耗。今后的工作還應繼續(xù)優(yōu)化電路結構,穩(wěn)定電路的輸出狀態(tài),增強電路的抗干擾能力。

p2p機相關文章:p2p原理

評論