基于CPCI的嵌入式系統的電源設計

1 引言

嵌入式系統廣泛應用于控制和通信領域。而這些系統運行速度高,系統較復雜,常常集成超大規模FPGA器件、DSP器件、DDR存儲器以及各種接口電路。這對電源的輸出電壓值、功耗、電壓精度、上電順序以及電源完整性提出更高的要求。這里介紹一種基于CPCI的嵌入式單板計算機電源的設計方案。該設計主要應用于航空設備和軍用車載設備。

2 系統電源需求分析與器件造型

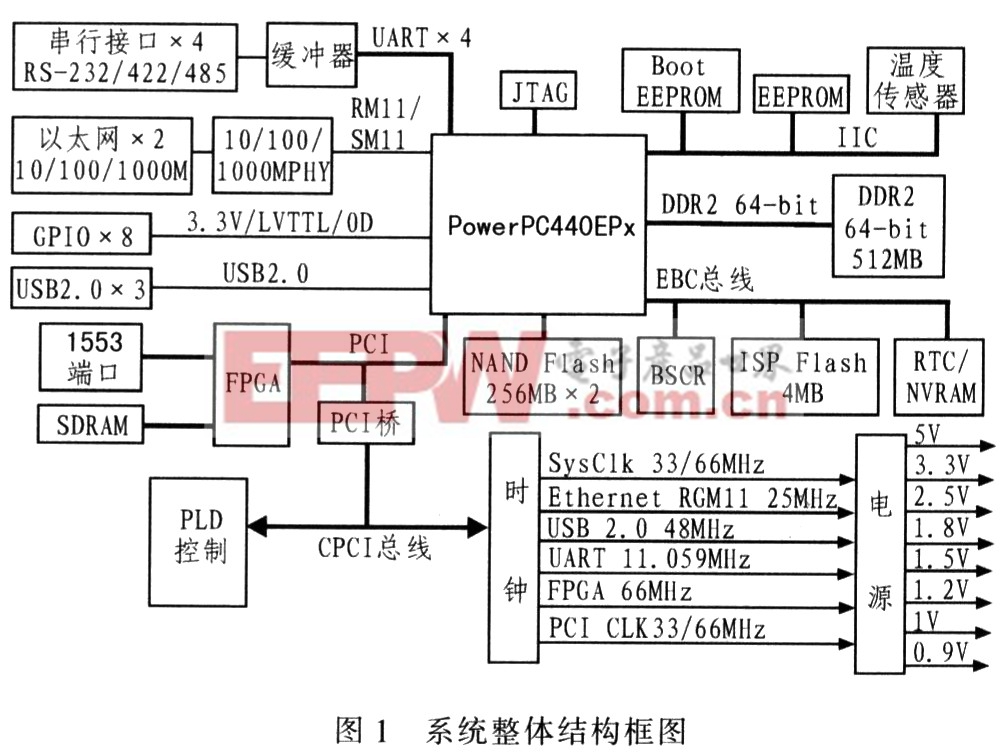

圖1為系統整體結構框圖。該系統由CPU和與其相連的DDR儲存器、PCI接口、時鐘、電源、EBC總線以及外部接口電路組成。CPU采用AMCC公司的PowerPC 440EPx。

2.1 系統電源需求

該系統電源較復雜,有多達8種不同的電源電壓值,其中5 V和3.3 V由CPCI機箱提供。5 V供給DC/DC器件降壓以產生其他電源電壓,同時給1553總線的變壓器供電。3.3 V是系統主電源,包括USB PHY、時鐘器件、FPGA和CPU以及PCI橋器件(PLX6466)的I/O部分等。其他電源電壓都是由5V或3.3 V經電源器件降壓得到。

評論