基于數據選擇器和D觸發器的多輸入時序電路設計

1 基本原理

1.1 基本多輸入時序網絡

1.1.1 多輸入時序網絡的基本形式

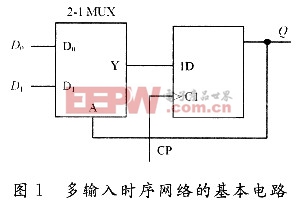

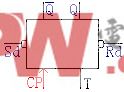

用1個D觸發器和1個2選1數據選擇器構成多輸入時序網絡的基本電路,如圖1所示。

圖1中,觸發器的現態輸出Qn作為數據選擇器的A選擇輸入變量,數據選擇器的Y輸出作為觸發器的D輸入信號,數據選擇器的輸入端D0,D1作為所構成時序網絡的外部信號輸入端。

1.1.2 多輸入時序網絡基本電路的狀態方程

由D觸發器的特性方程Qn+1=D、數據選擇器的輸出邏輯表達式![]() 的關系,得多輸入時序網絡基本電路的狀態方程:

的關系,得多輸入時序網絡基本電路的狀態方程:

![]()

寫成矩陣形式為:

1.1.3 已知狀態轉換關系確定時序網絡輸入矩陣參數的方法

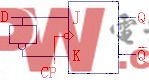

由式(1)、式(2)有:

(1)現態Qn=0時,Qn+1=D0,選擇輸入D0,由狀態轉換關系確定D0。可實現所要求的狀態轉換:

若Qn+1=O,即狀態轉換為0→O,則式(2)中的輸入矩陣應填D0=0;

若Qn+1=1,即狀態轉換為O→1,則式(2)中的輸入矩陣應填D0=使狀態產生變化的輸入變量。

評論