基于PCI總線的塔康視頻信號產生電路設計

PCI總線具有支持多種外圍設備、獨立于處理器、數據傳輸快等優點,已經應用于PC機,工控機等多種場合,如數據采集卡,IO控制卡、總線卡等都采用了PCI總線結構。在某綜合測試系統設計時,為提高系統集成化、模塊化的要求,設計研制了基于PCI9054的塔康(TACAN)視頻信號產生板卡。

1 系統組成及設計要求

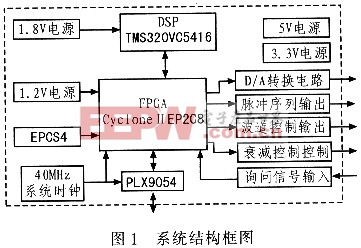

該系統主要由電源、PCI接口、FPGA邏輯、DSP、D/A轉換等電路組成。其中,電源電路為整個電路板提供電源,PCI接口電路提供PC機和電路板進行信息交互的通道,FPGA負責整個電路系統的邏輯,DSP電路負責整個電路系統的數據運算,D/A轉換電路將DSP產生的包絡數據轉化為模擬信號。塔康視頻信號產生電路的系統結構如圖1所示。

塔康視頻信號產生電路的工作流程為:PC通過PCI接口電路發送控制指令,FPGA通過PCI9054器件接收控制指令并把指令信息傳遞DSP,DSP接收到指令信息后,產生相應操作,D/A轉換電路將DSP產生的包絡數據轉化為模擬信號傳遞出來。塔康視頻信號產生電路將產生符合要求的正弦包絡信號和基準信號。其中,正弦包絡信號主要包含15 Hz正弦包絡信號和135 Hz正弦包絡信號,其函數式為:

![]()

式中,f=15 Hz,A0為直流成分,A1、A2分別為15 Hz正弦包絡和135 Hz正弦包絡的幅度。同時,系統在產生15 Hz正弦包絡時還可以產生主基準脈沖群,在產生135 Hz正弦包絡時產生輔助基準脈沖群。通過基準脈沖群信號和正弦包絡的正斜率過零點之間的時間間隔在正弦包絡總時間中占有的比例關系,可確定方位信息。

結合某型塔康的測試需求,該系統的具體設計要求是:15 Hz和135 Hz正弦包絡的信號深度均可調,幅度調整的范圍都是O~40%,最小調整間隔為1%:15 Hz正弦包絡和135Hz正弦包絡的幅度之和在總包絡的幅度所占大小不超過40%;15 Hz正弦包絡的相位在0°~359.9°內可調整,最小調整間隔是0.1°,135 Hz正弦包絡的相位在0°~39.9°內可調整,最小調整間隔也是0.1°。

2 系統硬件電路設計

2.1 電源電路

電源電路的主要功能是為整個電路板系統提供電源。電源電路從PCI插槽中取用3.3 V和5 V電源,通過電壓轉換器LDlll7S18和LDlll7 S12可分別得到1.8 V和1.2 V電壓,供不同的器件使用。

2.2 PCI接口電路

PCI接口電路的主要功能是提供PC和塔康視頻信號產生電路進行信息交互的通道。選用PLX公司的PCI9054器件,該器件符合PCI本地總線規范2.2版,突發傳輸速率可達到132 MB/s,本地總線支持復用/非復用的32位地址/數據,支持主模式、從模式以及DMA傳輸方式。該器件可靠性高,易于開發,滿足系統的要求。

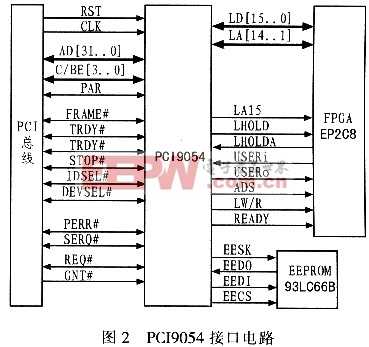

PCI9054通過引導EEPROM進行配置,其與串行EEPROM(IDT70261)的接口電路如圖2所示。PCI9054提供4個引腳與串行IDT70261相連接,它們分別是EEDI,EEDO,EESK,EECS,對應于IDT70261的DI,D0,SK,CS等4個引腳。在上電復位時,PCI9054會通過EEPROM中引導并對寄存器進行配置,完成命令控制和地址映射。

PCI9054局部總線的接口與DSP不完全兼容,需要通過FPGA實現數據的傳輸。因此在FPGA內部構建一個雙口RAM,PCI9054的局部數據線LD[15..0]、局部地址線LA[14..0]與FPGA直接相連,同時PCI9054的局部控制線也與FPGA直接相連,如圖2所示。

評論