加強ESD保護的技巧

LIC和LPORT

很多ESD器件數據手冊中經常提到讓器件盡可能靠近ESD輸入點。這樣LPORT/LIC比就會盡可能得低(即LIC>>LPORT)。LPORT的電感未必會影響整體的ESD性能,但LIC的電感則肯定會影響ESD性能。

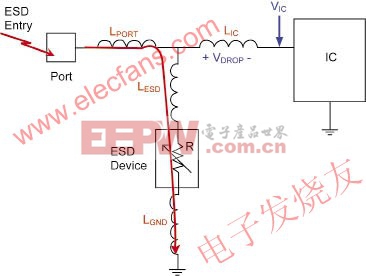

LIC的非線性會通過大幅削減IC電壓來充當ESD脈沖的初始峰值電流的緩沖器。隨著電感的降低(即ESD器件越來越靠近IC),電壓降也會不斷減小,直到無法獲得任何優勢時為止。所以,將LPORT/LIC比降至最低以便利用PCB跡線的寄生特性對設計者最有利。我們所說的電壓降如圖4所示。

圖4

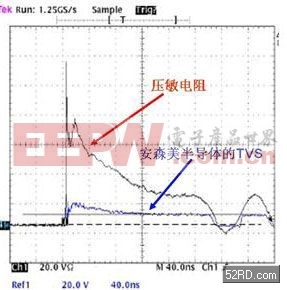

利用LIC和LPORT是提升整體ESD性能的直接方法。然而,無論上述比值有多小,仍然有設計會過早地出現故障。換句話說,LIC未能為峰值ESD電流提供充足的緩沖。

有時候,采用先前的技術不足以為給定電路板設計提供最大限度的ESD保護。原因在于流經“片上”ESD結構的電流過多,并且在I/O短接至GND或VCC時被損壞。

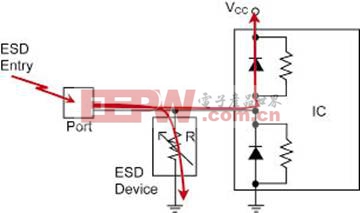

圖5有助于將它弄清楚,表明ESD器件和受保護的IC實際上共同承擔了來自于ESD脈沖的電流負載。該數值(負跡線電感)對應于正ESD脈沖,其中保護器件吸收了大多數電流,但是它本質上是一個帶有IC的電阻分壓器。

圖5

如圖5所示,IC上的軌對軌二極管負責將剩余的或“允通”電流導入VCC(它一般會通過旁路電容器回到GND)。很難確定什么樣的等效電阻適于為IC實現ESD保護,但是無疑比板上ESD器件高得多。

電機保護器相關文章:電機保護器原理 紅外熱像儀相關文章:紅外熱像儀原理

評論