低功耗10位100 MHz流水線A/D轉換器設計

摘要:介紹了一個10位100 MHz,1.8 V的流水線結構模/數轉換器(ADC),該ADC運用相鄰級運算放大器共享技術和逐級電容縮減技術,可以大大減小芯片的功耗和面積。電路采用級聯1個高性能前置采樣保持單元和4個運放共享的1.5位/級MDAC,并采用柵壓自舉開關和動態比較器來縮減功耗。結果顯示,在輸入頻率達到奈奎斯特頻率范圍內,整個ADC的有效位數始終高于9位。電路使用TSMC O.18 μm 1P6M CMOS工藝,在100 MHz的采樣頻率下,功耗僅為45 mW。

關鍵詞:流模/數轉換器;運放共享;柵壓自舉開關;動態比較器

O 引言

在混合信號集成電路系統中,模/數轉換器(ADC)是一個關鍵的模塊。許多現代應用,如數字便攜設備、視頻處理及無線通信等,都要求具有高采樣率、低功耗的模/數轉換器。同時,由于許多模/數轉換器被使用在電池供電的便攜式設備中,降低其功耗就變得越加重要。對于10 b,1 MSPS以上的ADC系統而言,流水線結構是一種合適的設計方案。在此闡述了能夠滿足10位精度、100 MHz采樣率的流水線結構ADC,并且運用了相鄰兩級共用一個運放的運放共享技術和逐級電容縮減技術來減小功耗和面積。該模/數轉換器中采用了低功耗增益提高運算放大器和動態比較器等元件,也更好的降低了功耗。

1 ADC電路結構

1.5位/級結構的ADC具有許多優點,首先每級多產生一位冗余位來進行數字冗余修正,大大減小比較器失調造成的影響。其次較小的單級分辨率可以獲得較高的速度。1.5位/級結構的單級閉環增益為2,開關電容電路可以具有較小的負載電容和反饋因子,因此每級可以獲得較大的帶寬。所以本電路采用1.5位/級級聯的結構。

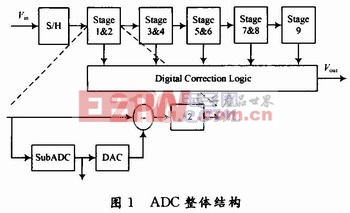

圖1為本文所采用的流水線ADC結構,采用了每級1.5位流水線級級聯。最前端是一個高性能采樣保持電路,雖然采樣保持電路需要消耗大量的功耗,但它能夠較好地減小由于MDAC和子ADC之間的采樣信號失配造成的孔徑誤差,可以使得電路性能得到較大提高。依次級聯8個相同的1.5位/級結構MDAC,最后一級是一個2位的FLASH ADC。所得到的18位數字輸出依次經過時間對齊電路和數字校正電路,經過數字校正后得到所需要的10位數字輸出。

如圖1所示,電路采用相鄰級運算放大器共享技術,后面的8個MDAC僅需要4個運算放大器。為了更好地降低功耗,電路使用了逐級電容縮減技術。電路中的Stage 1&2和Stage 3&4采用了相同的運算放大器,Stage 5&6和Stage 7&8進行了縮減,縮減因子為0.7。

1.1 采樣保持電路結構

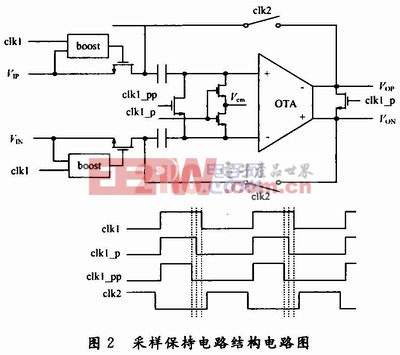

圖2為電容翻轉型采樣保持電路的結構圖。相對于電荷轉移型的采保電路,這種結構具有較大地反饋系數和較少的電容,使得電路具有實現面積小,噪聲低,功耗低,保持相建立時間短等優點,因而更適合于高速的流水線ADC。

該電路工作在采樣和保持2個階段:采樣階段,clkl,clkl_p,clkl_pp為高電平,clk2為低電平,此時輸入信號存儲在電容上,clkl_PP先于clkl_p和clkl截止,clkl_p先于clkl,采用2個提前截至的時鐘波形是為了減小圖中采樣開關的溝道電荷注入的影響。保持階段,clkl,clkl_p,clkl_PP為低電平,clk2為高電平,存儲于采樣電容的電荷傳輸至采樣保持電路的輸出并驅動下級負載。該電路的閉環增益為1。

由于開關的開關電阻和電荷注入會對電路產生巨大的影響,圖2中的輸入采樣開關采用了柵壓自舉開關,這樣可以較大的避免與輸入信號相關的電荷的注入。

評論