500兆/秒高速A/D系統的實現

摘要:介紹采樣率為500兆/秒、采樣精度為8bit的高速A/D系統的設計結構以及高速電路設計中的問題,最后還討論了如何在Windows95下設計具有實時性要求的程序。

本文引用地址:http://www.j9360.com/article/179084.htm關鍵詞:高速A/D變換 高速電路設計 Windows95 實時程序設計

在現代雷達系統、激光測距以及高能物理試驗中往往產生寬帶信號或者上升沿比較陡的信號(一般10ns左右)。若對此類信號進行數字化處理,要求A/D部分的采樣率至少應該在200M/s以上。本文介紹的系統正是針對這樣的要求而開發出來的。

1 系統結構

系統分為A/D轉換和數據傳輸控制兩大部分(圖1)。數據傳輸控制部分作成PC機的插卡在計算機的PCI擴展插槽內,它的主要功能是將A/D采樣得到的數據傳遞給計算機,同時產生相關的控制信號去控制整個系統;A/D轉換部分由于受到電源和體積的影響單獨作成一個模塊置于計算機外部,其中關鍵的核心器件ADC采用的是MAXIM公司推出的MAX101A,它的最高采樣率可達500兆/秒,采樣精度為8bit。兩部分之間的數據傳遞通過扁平電纜來完成。

2 A/D轉換

2.1信號調理

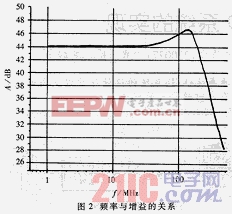

對于高速A/D采樣電路來講,前端調理電路顯得尤為重要,不僅要有足夠的帶寬,而且還要將單端的輸入信號變成差分信號提供給ADC,以減少偶次諧波的產生,同時本身的噪聲也要很小,這樣才不會對ADC的精度產生影響。考慮到上述因素,在前端部分采用了AD公司的AD8138作為緩沖放大器,它的性能指標為:-3dB帶寬320MHz,輸入噪聲5nV/(根號Hz)。AD8138為表面封裝器件,本身的體積非常小巧,使得ADC與信號輸入點的距離可以很近,大大減少了外界噪聲的影響。經測試,器件的模擬帶寬為230MHz(圖2)。

評論