一種全集成型CMOS LDO線性穩壓器設計

3 仿真驗證

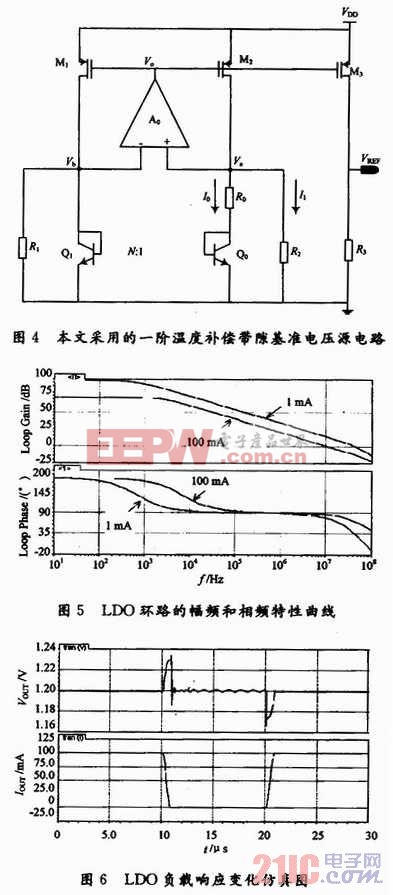

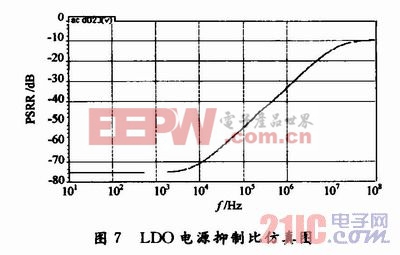

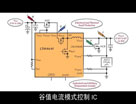

該電路采用SMIC 0.25μm CMOS工藝實現,輸入電源電壓為2.5 V,輸出電壓為1.2 V,作為芯片模擬部分的電源。LDO的環路穩定性采用Spectre stb仿真,結果如圖5所示,負載電流從1 mA變化到100 mA,整個系統相位裕度均在40°以上,系統穩定。圖6為負載電流從1 mA到100 mA轉換時,輸出電壓和輸出電流瞬態響應曲線。從圖中可以看出,瞬態響應過沖小于20 mV,無振鈴現象產生。圖6為仿真的電源電壓抑制比(PSRR)。低頻時PSRR好于75 dB。整個LDO包括基準電壓源共消耗靜態電流390 μA。

4 結語

本文設計了一種全集成型LDO線性穩壓器,采用一種簡單的頻率補償電路,通過輸出反饋電路引入零點,抵消了LDO產生第二個極點,獲得較好的穩定性。此方法結構簡單、不損失環路開環增益、帶寬高,而且所需要的補償電容小,節省芯片面積和輸出引腳。

評論