基于Protel 99 SE環境下PCB設計規范與技巧的研究

3 布線

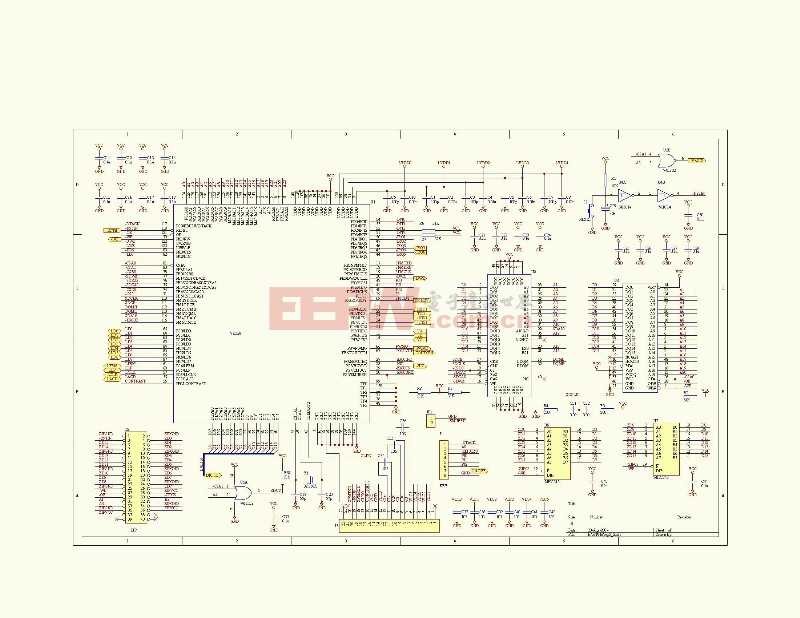

一個好的布局是重要的,但是一個好的布局只是為PCB板圖的設計打下了一個好的基礎,布線是整個PCB設計中最重要的工序。這將直接影響著PCB板的性能好壞。在PCB的設計過程中,布線一般有這么三種境界的劃分:首先是布通,這時PCB設計時的最基本的要求。如果線路都沒布通,搞得到處是飛線,那將是一塊不合格的板子,可以說還沒入門。其次是電器性能的滿足。這是衡量一塊印刷電路板是否合格的標準。這是在布通之后,認真調整布線,使其能達到最佳的電器性能。接著是美觀。假如你的布線布通了,也沒有什么影響電器性能的地方,但是一眼看過去雜亂無章的,加上五彩繽紛、花花綠綠的,那就算你的電器性能怎么好,在別人眼里還是垃圾一塊。這樣給測試和維修帶來極大的不便。布線要整齊劃一,不能縱橫交錯毫無章法。這些都要在保證電器性能和滿足其他個別要求的情況下實現,否則就是舍本逐末了。布線時主要按以下原則進行:

(1)一般情況下,首先應對電源線和地線進行布線,以保證電路板的電氣性能。在條件允許的范圍內,盡量加寬電源、地線寬度,最好是地線比電源線寬。還有就是遵守“20H規則”,由于電源層和地層的電場是變化的,在板的邊緣會向外輻射電磁干擾,稱為邊緣效益。這樣我們通過將電源層內縮,使得電場只在接地層的范圍內傳導,以一個H(電源和地之間的介質厚度)為單位,若內縮20H則可以把70%的電場限制在接地層邊沿內。

(2) PCB設計中應避免產生銳角和直角,盡可能采用45°的折線布線,不可使用90°折線,以減小高頻信號的輻射,要求高的線還要用雙弧線。

(3)器件去耦規則:在PCB板上增加必要的去耦電容,濾波電源上的干擾信號,使電源穩定。在多層板中,對去耦電容的位置一般要求不太高。但對雙層板,去耦電容的布局及電源布線方式等直接影響到整個系統的穩定性,一般應該使電流先經過濾波電容再供器件使用,同時還要充分考慮到期間產生的電源噪聲對下游的器件的影響,一般來誰,采用總線結構設計的電源模式;

(4)為防止不同工作頻率的模塊之間的互相干擾,一般盡量縮短高頻部分的布線長度,同時對模擬與數字電路應分別布置在PCB板的兩面,分別使用不同的層布線,中間用地層隔離的方式。

(5)振蕩器外殼接地,時鐘線要盡量短,且不能引得到處都是。時鐘振蕩電路下面、特殊高速邏輯電路部分要加大地的面積,而不應該走其它信號線,以使周圍電場趨近于零;

(6)預先對要求比較嚴格的線(如高頻線)進行布線,輸入端與輸出端的邊線應避免相鄰平行,以免產生反射干擾。必要時應加地線隔離,兩相鄰層的布線要互相垂直,以避免平行走線容易產生寄生耦合和層間的竄擾。

(7)設計布線時應讓布線長度盡量短,以減少由于走線過長帶來的干擾為問題,特別是一些重要信號線,如時鐘線,務必將其振蕩器放在離器件很近的地方。一般不要出現一端浮空的布線,以避免出現“天線效應”,減少不必要的干擾輻射和接受,否則帶來不可預知的結果;

(8)任何信號線都不要形成環路,如不可避免,環路應盡量小,這樣對外的輻射越少,接收外界的干擾也越小。信號線的過孔要盡量少,關鍵的線盡量短而粗,并在兩邊加上保護地來盡量減小信號的回路面積。

最后要進行布線優化和絲印,俗話說“沒有最好的,只有更好的”,不管你怎么挖空心思的去設計,等你畫完之后,再去看一看,還是會覺得很多地方可以修改的。一般設計的經驗是:優化布線的時間是初次布線的時間的兩倍。感覺沒什么地方需要修改之后,就可以鋪銅了(Pla-ce->polygon Plane)。鋪銅一般鋪地線(注意模擬地和數字地的分離),多層板時還可能需要鋪電源。對于絲印,要注意不能被器件擋住或被過孔和焊盤去掉。同時,設計時正視元件面,底層的字應做鏡像處理,以免混淆層面。

4 設計評審

PCB板圖設計完成后,根據相應的質量評審要求,對設計進行設計評審。評審的內容大體分為下面幾個方面:

(1)檢查定位孔、定位件等機械尺寸是否與結構圖一致。(2)檢查高頻、高速、時鐘等易受干擾的信號線,是否回路面積最小、是否遠離干擾源,是否有多余的過孔和繞線、是否跨地層分割區。(3)檢查晶體、變壓器、光耦、電源模塊下面是否有信號線穿過,應盡量避免在其下面穿線,特別是晶體下面應盡量鋪設接地的銅皮。 (4)檢查器件的序號是否有序排列,絲印標示等是否覆蓋焊盤、過孔等。(5)檢查布線完成情況是否百分之百,是否有線頭,是否有孤立的銅皮。本文引用地址:http://www.j9360.com/article/178711.htm

評論