基于集成計數器的N進制計數器設計與仿真

摘要:計數器是一種重要的時序邏輯電路,廣泛應用于各類數字系統中。介紹以集成計數器74LS161和74LS160為基礎,用歸零法設計N進制計數器的原理與步驟。用此方法設計了3種36進制計數器,并用Multisim10軟件進行仿真。計算機仿真結果表明設計的計數器實現了36進制計數的功能。基于集成計數器的N進制計數器設計方法簡單、可行,運用Multisim10進行電子電路設計和仿真具有省時、低成本、高效率的優越性。

關鍵詞:電路設計;仿真;計數器;歸零法;Multisim10

計數器是記憶時鐘脈沖個數的數字電路,作為一種最典型的時序邏輯電路,在各類數字系統中有著廣泛的應用。計數器的設計方法主要有兩種,1)以時鐘觸發器為核心加上必要的門電路進行設計;2)利用集成計數器構建,這種方法從設計原理到硬件實現都相對簡單,因而較為常用。基于集成計數器的N進制計數器設計方法有歸零法和置數法。文中以最常用的4位二進制(十六進制)同步加法計數器74LS161及十進制同步加法計數器74LS160為核心,以三十六進制為例,介紹了歸零法設計N進制計數器的方法,并用Multisim10軟件進行仿真。Multisim10軟件由美國國家儀器(National Instruments,NI)公司于2007年推出,該軟件具有以下特點:1)直觀的圖形界面;2)龐大的元器件庫;3)豐富的測試儀器;4)完備的分析工具;5)強大的仿真能力;廣泛應用于電子電路的教學、設計和科研中。

1 歸零法設計原理

1.1 集成計數器功能描述

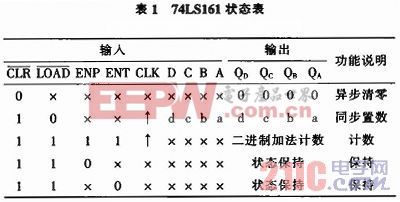

集成計數器由芯片廠家生產后,其功能已固化在集成芯片中,其功能常用狀態表描述。表1是4位二進制同步加法計數器74LS161的狀態表,表中![]() 是異步清零控制端,低電平有效;

是異步清零控制端,低電平有效;![]() 是同步置數控制端,低電平有效;ENP和ENT是計數器工作狀態控制端,高電平計數;CLK是計數脈沖輸入端;D、C、B、A是并行數據輸入端;QD、QC、QB、QA是計數器狀態輸出端;“×”表示任意狀態,“↑”表示時鐘脈沖上升沿。

是同步置數控制端,低電平有效;ENP和ENT是計數器工作狀態控制端,高電平計數;CLK是計數脈沖輸入端;D、C、B、A是并行數據輸入端;QD、QC、QB、QA是計數器狀態輸出端;“×”表示任意狀態,“↑”表示時鐘脈沖上升沿。

十進制同步加法計數器74LS160的狀態表與74LS161類似,區別在于計數狀態是按十進制(8421BCD碼表示)規律變化。

1.2 歸零法設計原理

設現有M進制集成計數器,設計N進制計數器。若M>N,從全零初始狀態S0開始計數,第1個時鐘到來時,計數狀態為S1,第N-1時鐘到來時,計數狀態為SN-1,第N時鐘到來時,利用集成計數器的清零端或是置數端,使計數狀態返回全零初始狀態S0,原M進制集成計數器中的SN~SM-1這M-N個狀態被跳過。若集成計數器的清零端為異步控制方式,具體設計與仿真步驟為:

1)確定最大計數狀態SN(過渡狀態),并寫出SN的二進制代碼:

2)根據狀態SN的非完全譯碼,求歸零邏輯,即清零端控制信號的邏輯表達式;

3)在仿真平臺Multisim中選擇器件,根據歸零邏輯創建仿真電路;

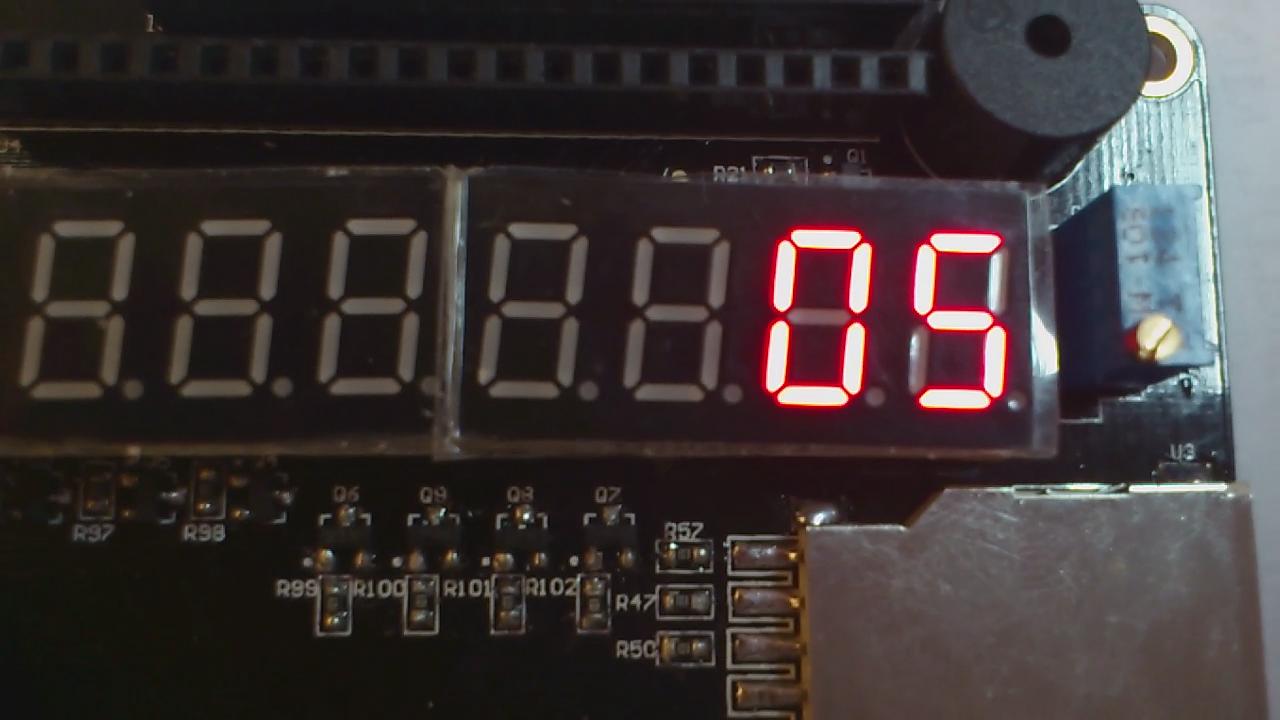

4)選擇時鐘信號源輸入,示波器或數碼管等作為測量或顯示儀器,運行仿真電路,觀測結果。

評論