混合型多電平逆變器電路設計分析

1、引言

本文引用地址:http://www.j9360.com/article/176839.htm多電平逆變器由于輸出電壓du-dt小、諧波含量低等優點,在高壓大功率變換領域得到廣泛應用[1,2]。級聯型多電平逆變器是最早的多電平逆變結構,1980年出現了二極管箝位型多電平逆變器[3],1992年,T.A. Meynard提出了電容箝位型多電平逆變器[4]。由于級聯型多電平逆變器不存在直流側電容電位不平衡問題、控制簡單,以及器件較少等優點,近十幾年來得到廣泛的應用。

混合型多電平逆變器是最近發展起來的一種有效的多電平改進模式,該電路由級聯型多電平逆變電路發展而來,且主電路是單元級聯式結構,因此可用較少的元件數量實現盡可能多的電平數,從而降低了系統成本,減小了輸出電壓的諧波總含量(THD)。按實現電路方式的不同,本文將混合型多電平逆變器分為各級聯單元電壓等級不同的混合電平式逆變器[5,6]和各級聯單元拓撲結構不同的混合單元式逆變器[7],并分析了這兩類逆變器電路結構的特點。針對這兩類混合型多電平逆變器存在高壓單元功率器件電壓應力過高、低壓單元電流倒灌的問題,本文提出了一種有效的主電路拓撲結構設計方法。

2、混合電平式逆變器拓撲結構分析

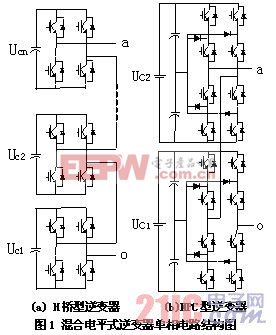

圖1(a)給出了單相n階級聯型多電平逆變器拓撲結構,當直流側電壓Uci(i=1,2…n)不相等(一般是成倍關系)[5,6] ,則可稱為H橋混合型多電平逆變器。將最低等級的電壓記為E,單元間電壓比取值不同,逆變器輸出相電壓Vao電平數不同,為了使一定數量的逆變單元輸出電平數最多,同時輸出電壓各電平臺階階躍限定為1E,文獻[7]給出最大延伸原理,相鄰逆變單元電壓最大比值可按下式選取:

其中,ni指第i個H逆變單元輸出電平數量

各逆變單元電壓滿足以下條件[8]:

此時,相電壓Vao可輸出的電平數為每個級聯單元的電平數的乘積,如下式:

H橋混合型逆變器由于每個H橋逆變單元可產生-VDC、0、VDC三個電平,由1式可知,電壓最大比值為1:3。逆變器輸出相電壓Vao可表示為SE,其中S為逆變器輸出電平數,當電壓等級之比為1:1,輸出電平數為2n+1;電壓等級之比為1:2,輸出電平數為2n+1-1;電壓等級之比為1:3,輸出電平數為3n。不同電壓比時,逆變器所用功率器件數均為4n。

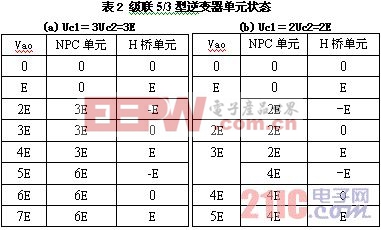

以兩逆變單元級聯為例,每個H橋逆變單元可以輸出3個電平,其數學描述為n1=3,n2=3,n=2,根據公式1和3可得,當Uc2=3Uc1=3E 時,輸出可達最大電平數N=3×3=9。但每一個輸出合成電壓電平所對應的兩個單元的輸出是唯一的,由表1(a)給出相電壓為正時的各單元電平輸出狀態可知,沒有冗余的狀態。如果 Uc2的直流母線端采用二極管不可控整流,在相電壓輸出為2E時,逆變單元2輸出為3E,而逆變單元1輸出為-1E,出現逆變單元2將其變換的電能一部分注入到了逆變單元1,另一部分能量輸送給負載,即產生電流倒灌問題,從而導致電容電壓不平衡,這種情況是顯然不希望出現的。為了獲得更多的冗余狀態,則必須減少Uc2與Uc1的比值,可選用Uc2=2Uc1。表1(b) 給出了Uc2=2Uc1=2E時輸出電壓的合成情況,顯然輸出電壓從9電平降為了7電平,但多出了一些冗余狀態,從而可以根據負載電流的方向,來選擇不同的狀態組合,以避免出現電流倒灌現象。

H橋混合型逆變器在給定逆變單元數量的基礎上,可大大提高輸出電壓電平數量。但由于電壓以2S、3S倍數增加,而功率器件的耐壓有限,所以H橋混合型逆變電路的串聯級數不能無限增加,實際系統的級聯數目多不會超過3。

在級聯型逆變器研究的基礎之上,文獻[9]提出一種采用NPC逆變H橋五電平單元作為逆變單元的多電平拓撲結構,文獻[10]將此改進成NPC混合型逆變器,如圖1(b)所示。由于NPC全橋逆變單元可產生五種電平,由式1和式3可知,最大電壓等級比為1:5,Vao電平數可達25,大大提高了輸出電壓的電平數目。同樣方法分析可知,當電壓比為1:4和1:5時,該逆變器也會產生電流倒灌現象。為了避免電流倒灌現象,該電路最大電壓比為1:3,單相輸出電平數為17。相對于H橋混合型逆變器,該電路減少了直流電源的數目,但增加了功率器件數量及控制復雜度。

3、混合單元式逆變器拓撲結構分析

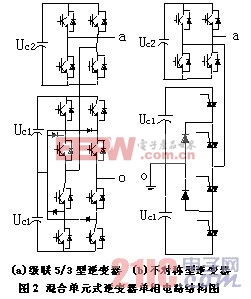

在混合電平式逆變器研究的基礎之上,文獻[7]提出將NPC逆變H橋單元與傳統逆變H橋單元級聯的5/3型混合單元式拓撲結構方案,如圖2(a)所示,NPC全橋逆變單元可有效克服逆變器高壓單元電壓應力過高的缺點。NPC全橋逆變單元可輸出5種電平,傳統H橋單元可輸出3種電平,其數學描述為n1=5,n2=3,n=2,根據公式1和3可得,當Uc1=3Uc2=3E時,輸出可達最大電平數N=5×3=15,表2(a)給出相電壓為正時的各單元電平輸出狀態。若Uc1的直流母線端采用二極管不可控整流,在相電壓輸出為2E或4E時,會出現NPC全橋單元將其變換的電能一部分注入到了H橋單元,另一部分能量輸送給負載,即產生電流倒灌問題。為了獲得更多的冗余狀態,則必須減少Uc1與Uc2的比值,文獻[7]選用Uc1=2Uc2,表2(b)給出了Uc1=2Uc2=2E時輸出電壓的合成情況,雖然輸出電壓從15電平降為11電平,但由于多出了一些狀態,從而可根據負載電流的方向來選擇不同的狀態組合,以避免出現電流倒灌現象。但該電路使用器件較多。

文獻[11]提出了基于NPC三電平變換單元與H橋變換單元級聯的不對稱型逆變器(Asymmetric Inverter),單相拓撲結構如圖2(b)所示。該電路高壓NPC逆變單元采用的是 IGCT 器件,低壓H橋單元器件采用的是IGBT 開關器件。其中高壓3電平NPC逆變單元是主要逆變電路,Uc1為3E,這部分電路給輸出提供了主要的電平電壓和大部分輸出功率,因此將NPC逆變單元稱為主逆變單元;低壓的 H 橋逆變電路單元則是輔助逆變電路,Uc2為E,這部分電路給輸出提供了輔助改善波形的電平電壓和小部分輸出功率,因此將這部分逆變電路稱為輔助逆變單元。在功率器件選用上,該電路采用了一種組合的方法,同時利用了兩種不同開關器件的優點:IGCT的高阻斷能力和IGBT的快速開關能力。但該電路在相電壓輸出為+2E或者-2E時,輔助逆變單元將輸出對應的反相電壓-1E或者+1E,在有功應用中,也會出現電流倒灌現象。如果Uc1為2E,Uc2為E,則可避免電流倒灌現象。

4、混合型逆變器拓撲結構設計方法要點

由前面分析可知,混合型逆變器存在高壓單元電壓應力過高、低壓單元電流倒灌的問題。為了解決以上問題,在設計時可從以下兩方面進行改進:

(1)克服高壓單元功率器件電壓應力過高問題

選擇高阻斷能力器件(如IGCT、GTO)或選擇二極管箝位型逆變單元作為高壓逆變單元(如二極管箝位型三電平或五電平結構)。這兩種方法均可克服高壓單元功率器件電壓應力過高的問題,但由于高阻斷能力的功率器件成本高、開關頻率低,從而影響了系統的成本及輸出波形的質量,而在逆變單元電壓等級一定的情況下,NPC逆變臂功率器件的電壓應力卻是H橋單元的一半,可以顯著降低功率器件的電壓應力。因此,選擇二極管箝位型逆變單元作為高壓逆變單元是一種更加值得推薦的方法。

(2)消除低壓單元電流倒灌問題

由于混合型逆變器在選取電壓比較大時,會產生電流倒灌現象,因此在設計過程中,可選取適當的電壓比以提供消除電流倒灌現象所需的冗余狀態,并使得各電平臺階階躍也限定在1E之內。以圖2(b)電路為例,采用Matlab對該電路進行了仿真,仿真結果如圖3,其中調制波頻率為50Hz。根據公式(1)可知,兩逆變單元電壓關系可為Uc1=3Uc2 =3.3kV和Uc1=2Uc2 =3.0kV兩種情況,相電壓Vao輸出分別為9電平和7電平(如圖3(a)),兩種情況單元1和單元2輸出電壓波形如圖3(b)和圖3(c)。從圖3(c)可看出,當Uc1=3Uc2,單元1輸出電壓為正時,單元2輸出電壓為1.1kV、0kV、-1.1kV三種情況,在單元2輸出-1.1kV時,則會與單元1輸出3.3kV電壓形成環流,出現電流倒灌現象,降低了逆變器輸出功率,并導致單元2直流側電位平衡,增加了輸出相電壓Vao的諧波含量(如圖3(d)所示,THD為6.58%),降低了Vao的質量;而Uc1=2Uc2時,雖然Vao為7電平,但從圖3(b) 與圖3(c)看出,不會出現電流倒灌現象,Vao的THD降至3.51%。

以上分析及仿真結果表明:Uc1=2Uc與Uc1=3Uc2相比,在輸出相電壓Vao大致相同(分別為4.5kV和4.4 kV)的情況下,雖然Vao從9電平降為7電平,但低次諧波的幅值卻顯著降低,輸出電壓的質量得到了較大的提高(THD從6.58%降至3.51%),高壓單元功率器件電壓應力也有所下降(從1.65kV降至1.5kV)。

5、結論

本文針對混合電平式逆變器和混合單元式逆變器存在的高壓單元功率器件電壓應力過高、低壓單元電流倒灌的問題,提出了高壓單元采用二極管箝位型拓撲結構,選取各單元適當電壓比的設計方法,經分析及仿真實驗表明,該方法在克服電壓應力過高、消除低壓單元電流倒灌方面是有效的。

參考文獻:

1.Rodriguez.J,Lai.J.S,Peng.F.Z. Multilevel Inverters:A Survey of Topologies, Control, and Applications[J]. IEEE Trans Indus Electron, 2002,49(4):724-737

2.Tolbert.L.M, Peng.F.Z,, Habetler.T.G. Multilevel converters for large electric drives[J]. IEEE Trans. Ind. Applicat. 1999,35(1):36-44

3.A. Nabae, I. Takahashi, and H. Akagi, A New Neutral-Point Clamped PWM Inverter[A], IEEE IAS. 1980:761-766.

4.T.A. Meynard, H. Forch. Multi-level conversion: high voltage choppers and voltage-source inverters[A]. IEEE PESC 1992:397-403

5.Madhav D. Manjrekar, Thomas A. Lipo. A hybrid multilevel inverter topology for drive applications[A]. IEEE APEC 1998:523-529.

6.T. A. Lipo and M. D. Manjrekar. Hybrid topology for multilevel power conversion [P]. U. S. Patent 6005788, 1999

7.Keith Corzine, Yakov Familiant. A New Cascaded Multilevel H-Bridge Drive[J], IEEE Trans. Power Electron, 2002,17(1):125-131

8.Cassiano Rech, Humberto Pinheiro, Hilton A. Gründling, etc. Analysis and comparison of hybrid multilevel voltage source inverters[A]. IEEE PESC 2002:491-496

9.M.R.Pavan Kumar, J.M.S.Kim, A hybrid multi-level switching converter for ring-magnet power supplies[J]. IEEE Trans. Nuclear Science, 1996, 43(3):1876-1883.

10.丁凱 鄒云屏 王展 吳智超等,一種適用于高壓大功率的新型混合二極管鉗位級聯多電平變換器[J].中國電機工程學報, 2004.24(9):62-67

11.Peter K. Steimer,Madhav D. Manjrekar. Practical medium voltage converter topologies for high power applications[A]. IEEE IAS 2001:1723-1730

評論