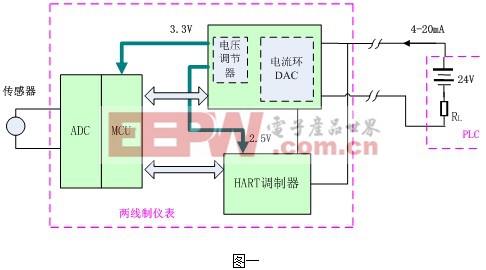

用于4~20mA電流環路的低成本HART發送器的設計

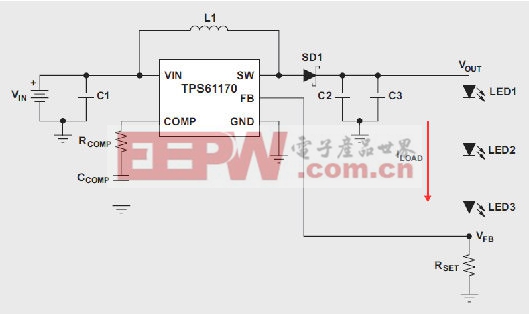

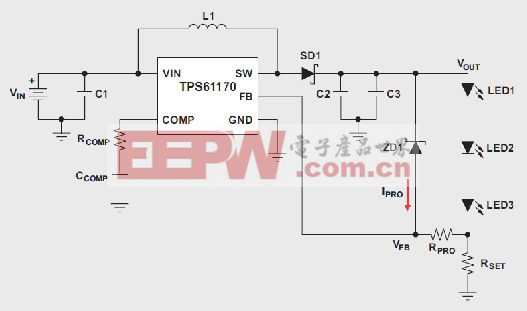

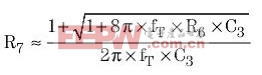

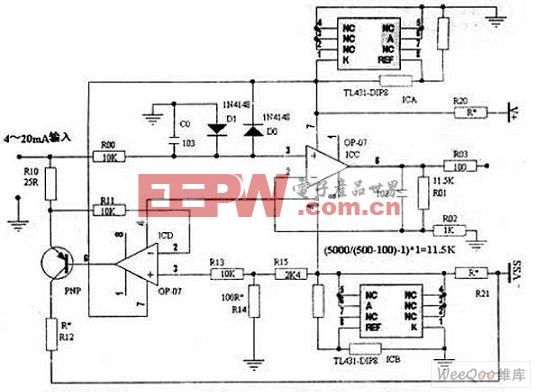

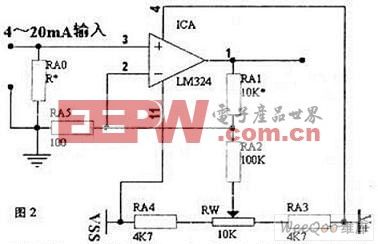

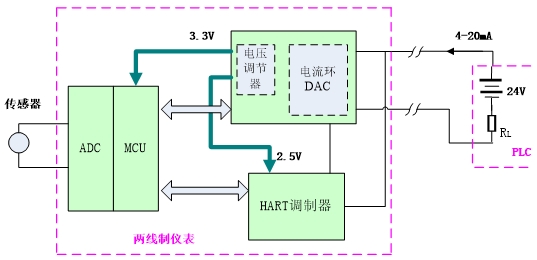

利用可尋址遠程傳感器數據通路(HART)協議,過程測量與控制器件可通過傳統4-20mA電流環路實現通信。這種協議使用1200 Hz和2200 Hz頻率的移頻鍵控(FSK)。此處,一個 1200Hz周期代表一個邏輯1,而兩個2200Hz周期代表邏輯0.由于FSK波形的平均值始終為0,因此模擬4-20mA信號不受影響。 理想情況下,FSK信號由疊加在DC測量信號上的兩個頻率正弦波組成。但是,相連續FSK正弦波的生成是一種十分復雜的過程。因此,為了簡化HART信號波形的生成過程,HART規范的物理層對參數極限值進行了定義,標準化波形的振幅、形態和轉換速率均不得超出這些參數極限值。在這種情況下,一種梯形波形非常適合于這種應用,圖1顯示了其各個極限值。 圖1:梯形HART電流波形的最小與最大值 圖2所示HART發送器提供了一種簡單且低成本的解決方案,其產生一個梯形HART波形,并將它疊加在一個可變DC電平上,最終把產生的輸出電壓轉換為電流環路。 HART FSK信號(常常由本地微控制器單元[MCU]生成),被應用于首個NAND柵極(G1)的輸入端。MCU的通用I/O端口的第二個輸出,起到一個有效高態“激活”(ENABLE)信號的作用。G1控制兩個遠端NAND柵極(G2和G3),其輸出通過高阻抗分壓器R1和R2連接到一起。 由R4和R5組成的第二個分壓器,將5V電源分為一個VREF = VCC/2的基準電壓,即2.5V.只要“激活”為低電平,G2的輸出便為低態,而G3輸出為高態。由于高阻抗負載,NAND輸出擁有軌到軌功能;R1=R2 時,A1非反向輸入VIN的輸入電壓也為2.5V. 當“激活”為高態時,G2和G3輸出相互換相,從而在VIN下形成一個小方波,其圍繞VREF對稱擺動。VIN的峰值到峰值振幅為: VS為正5V電源,而R1|| R2為R1和R2的并聯組合。 把圖2的電阻值插入方程式得到VIN(PP)=200Mv的輸入電壓擺動,其讓VIN擺動位于2.4V和2.6V之間。當VIN升至2.6V時,A1的輸出立即達到正飽和狀態,并通過R6和R7對C3充電。C3 (VHART) 的實際HART電壓線性上升,直到達到2.6V為止。這時,放大器A1迅速退出飽和狀態,并起到一個電壓跟隨器的作用,從而將VHART保持在2.6V.當VIN下降至2.4V時,A1輸出進入負飽和狀態,并通過R6和R7對C3放電。之后,VHART線性下降,直到其達到2.4V為止。這時,A1退出飽和狀態,并再次起到一個電壓跟隨器的作用,將VHART保持在2.4V. 由此產生的梯形波形在振幅方面與VIN相等,并且圍繞VREF做對稱擺動。它的轉換速率計算方法如下: 其中,VSAT為A1的正或負輸出飽和電壓。 由于VHART的AC電流比VSAT小,因此VHART可以由其靜態電平VREF得到近似值。另外,A1軌到軌輸出能力結合R6負載高阻抗,可得到5V和0V的輸出飽和電平。假設R7遠小于R6,則前面表達式可簡化為: 如果我們把圖2的R6和C3組件值插入方程式,則梯形波形的轉換速率結果為±1.25 V/ms. 把VHART (200Mv)的峰值到峰值振幅調節為1mA HART峰值到峰值電流信號,讓1.25V/ms電壓轉換速率相當于HART電流信號中6.25 mA/ms的電流轉換速率,從而完全位于圖1所示極限值范圍以內。 要求使用R7來將A1輸出隔離于大電容負載C3,目的是維持閉環穩定性。具體要求值取決于A1的單位增益帶寬fT以及R6和C3的值。R7的有效近似值計算方法如下: A1必須具有相當寬的頻率響應,并且其轉換速率要明顯快于HART梯形波形。OPA2374是TI一種低成本的雙運算放大器,其擁有5 V/μs的高轉換速率和fT = 6.5 MHz的單位增益帶寬。另外,放大器輸出具有軌到軌驅動能力,其典型靜態電流為每個放大器 585μA.

基爾霍夫電流相關文章:基爾霍夫電流定律

評論