利用快速、高精度SAR型模數轉換器延長電池壽命

隨著醫療、消費電子和工業市場上的便攜式手持儀器儀表日趨向尺寸更小、重量更輕、電池(或每次充電)續航時間更長、成本更低且通常功能更多方向發展,低功耗已經成為如今電池供電模數轉換器應用的一項關鍵要求。即使是在非電池供電的應用中,低功耗的好處也不容忽視,因為低功耗系統無需散熱器或風扇也能工作,因而尺寸更小、成本更低,而且更加可靠,同時也“更加綠色環保”。此外,許多設計人員在設計產品時都面臨一個挑戰,即在增強產品功能或性能的同時降低或者至少不得超過當前的功耗預算。

本文引用地址:http://www.j9360.com/article/175902.htm當今市場上品種繁多的ADC則使得選擇符合特定系統要求的最佳器件變得更加困難。如果說低功耗是必須的條件,那么除了評估速度和精度等常見的轉換器性能特性之外,還需要考慮更多性能指標。了解這些指標以及設計決策會對功耗預算有何影響,對于確定系統功耗和電池壽命計算非常重要。

ADC的平均功耗是轉換期間所用功耗、不轉換時所用功耗以及各模式下所用時間的函數,如等式1所示。

PAVG = 平均功耗。

PCONV = 轉換期間的功耗。

PSTBY = 待機或關斷模式下的功耗。

tCONV = 轉換所用時間。

tSTBY = 處于待機或關斷模式的時間。

轉換期間所用功耗通常遠大于待機功耗,因此如果處于待機模式的時間增加,平均功耗會顯著降低。逐次逼近(SAR)型轉換器尤其適合此類工作模式

影響系統電源使用情況的最大因素之一是板上電源的選擇。對于便攜式應用,系統通常由3 V紐扣式鋰電池直接供電。這樣就無需使用低壓差穩壓器,從而節省電能、空間和成本。非電池應用也可受益于具有低VDD電源電壓范圍的轉換器,因為功耗與輸入電壓成正比。為VDDADC選擇最低可接受VDDVDD將可降低功耗。

針對低功耗應用的所有ADC都具有關斷或待機模式,以便在閑置期間節省電能。ADC可以在單次轉換之間關斷,或者以高吞吐速率突發執行一陣轉換,在這些突發之間關斷ADC。對于單通道轉換器,工作模式的控制功能可以集成到通信接口,或者在完成一次轉換后自動進行。

將模式控制集成到通信接口的好處是可以減少引腳數量。這樣可以降低功耗,因為要驅動的輸入更少,同時漏電流也更小。此外,引腳數量越少,封裝尺寸也就越小,同時MCU所需的I/O也越少。無論采用何種控制方法,只要謹慎使用這些模式都能顯著節省電能。

顧名思義,關斷模式會關閉部分ADC電路,從而降低功耗。關斷后電路重新啟動轉換所需的時間決定可有效使用此類模式的吞吐速率。對于帶有內部基準電壓源的ADC,重新啟動時間將由基準電容重新充電所需的時間決定。采用外部基準電壓源的模數轉換器需要足夠的時間在重新啟動時正確跟蹤模擬輸入。

對于當今市場上的所有ADC,功耗均與吞吐速率成正比。功耗由靜態功耗和動態功耗組成。靜態功耗是恒定的,動態功耗則和吞吐速率呈線性變化關系。因此,在滿足應用要求的前提下盡可能選擇最低的吞吐速率可以省電。

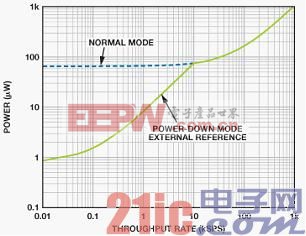

圖1所示為AD7091R,的典型功耗與吞吐速率的函數關系,該器件是ADI公司最近推出的超低功耗ADC。圖中還比較了利用器件的關斷模式(尤其是在較低吞吐速率條件下)可以帶來怎樣的額外省電效果。AD7091R的吞吐速率和關斷模式利用率取決于器件的重新啟動時間,以及基準電容的重新充電時間,因為AD7091R具有片內基準電壓源。基準電容重新充電所需的時間取決于電容大小,以及片內基準電壓源重新啟動時電容的剩余電荷水平。

圖1. AD7091R ADC功耗與吞吐速率的關系

ADC中啟動轉換請求的最常見方法是采用專用轉換輸入引腳或通過串行接口進行控制。采用專用輸入引腳(CONVST)時,轉換在下降沿啟動。然后,由片內振蕩器控制轉換,轉換完成后,可通過串行接口回讀結果。因此,轉換始終以恒定的最佳速度運行,允許器件在轉換完成時進入低功耗模式,從而節省電能。

當ADC中的采樣時刻由片選(CS)上的下降沿啟動時,轉換由內部采樣時鐘(SCLK)信號控制。SCLK頻率將會影響轉換時間和可實現的吞吐速率,進而影響功耗。SCLK速率越快,轉換時間就越短。轉換時間越短,器件處于低功耗模式的時間比例相對于正常模式就越大,因此可以實現顯著的省電效果。也就是說,如果每次轉換需要N SCLK周期,那么對于每秒執行S次轉換,SCLK開關的總時間為S S × N/fSCLK每秒內的靜態時間如等式2所示。

因此,對于給定的每秒采樣次數,隨著fSCLK增加,每秒內的靜態時間也會增加。

例如,假設完成轉換并讀取結果需要16個SCLK周期,則對于采樣速率為100 kSPS且SCLK為30 MHz的系統,靜態時間所占比例為94.67%,也就是說轉換所用時間占5.33%(每秒內53.3 ms)。當SCLK為10 MHz時,同一系統的靜態時間僅占84%,也就是說轉換用時為160 ms。因此,要實現最佳功耗性能,轉換器應以可支持的最高SCLK頻率工作。

針對低功耗應用而設計時,有個很重要的參數卻往往被忽視,即輸出引腳(尤其是SCLK、CS和SDO等通信接口引腳)上的容性負載,因為這些I/O變量會在轉換過程中不斷改變狀態。輸出端上的容性負載等于驅動器IC本身的引腳電容、輸入引腳的引腳電容以及PCB走線電容之和。走線電容通常都很小,處于飛法范圍內,因此意義不大。為容性負載充電所需的功率(PL)是負載(CL)、驅動電壓(VDRIVE)以及充電頻率(f)的函數,其定義如等式3所示。

因此,整個系統的功率等于負載電容(CLn)和開關頻率(fn)乘積之和乘以驅動電壓的平方。

評論