一種基于CPLD的可編程FV變換電路

摘要:文章介紹了一種可編程的頻率電壓變換電路(F/V),將頻率信號通過復雜可編程邏輯器件(CPLD)變換為與頻率成正比的脈寬信號,脈寬信號控制模擬開關對基準電壓信號進行斬波,斬波信號經低通濾波后輸出直流電壓信號。

關鍵詞:可編程邏輯器件;頻率電壓變換;脈沖寬度調制

0 前言

電氣自動化和過程自動化及自動檢測領域常常用到頻率電壓變換器F/V,需要將頻率信號轉換為電壓信號。F/V變換器的實現方法一般有3種:一是基于專用F/V轉換芯片(如LM331),二是基于模擬電路,三是基于微處理器和D/A轉換器。前兩種F/V變換器的共同缺點是量程單一,頻率變換范圍不能在線改變或不能方便地改變。第三種F/V變換器需要較高速度的微處理器和高分辨率D/A轉換器,成本較高。本文介紹一種基于CPLD的可編程F/V變換電路,該電路簡單、頻率變換范圍可任意連續設置、精度高,具有較好的實用價值。

1 電路的基本原理

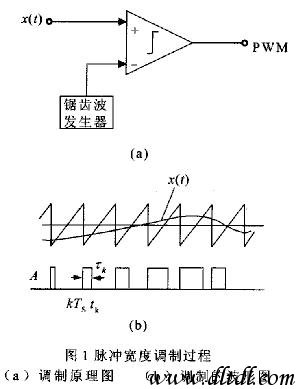

F/V變換電路的基本結構,頻率信號經K分頻電路轉換為占空比為50%的方波信號;方波信號經頻率/脈寬變換電路轉換為脈寬與頻率成正比的脈沖調寬信號;脈沖調寬信號的高電平控制模擬開關與電壓基準接通,低電平控制模擬開關與信號地接通,模擬開關的輸出經低通濾波器將脈沖寬度信號轉換為直流電壓信號。

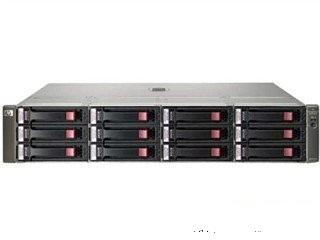

圖2為F/PWM變換電路的原理圖,fs為被變換頻率信號,f0為參考時鐘信號,D1為M分頻器,D2為K分頻器,C1、C2為n位二進制計數器,U1、U2為上升沿觸發的D觸發器。當K分頻器輸出fk為0時,計數C1器清零,U1觸發器的輸出置1,當fk為1時,計數器C1在M分頻器的輸出fc的作用下增量計數。當計數器C1計數由N-1變為N時,其計數器C1的Qn腳輸出由0變為1,觸發D觸發器1的輸出為邏輯0。當K分頻器輸出fk為1時,計數C2器清零,U2觸發器的輸出置1,當fk為0時,計數器C2在M分頻器的輸出fc的作用下增量計數。當計數器C2輸出由N-1變為N時,其計數器C2的Q腳輸出由0變為1,觸發D觸發器U2的輸出為邏輯0。兩組計數一觸發電路邏輯相反,經過邏輯組合輸出得到脈寬與頻率fk成正比的輸出波形fPWM。頻率脈寬變換時序圖如圖3所示。

設被變換頻率信號fs的周期為T,則K分頻信號fk的周期為KT,脈寬調制信號的寬度為τ,設計數器對fc的計數為N,則τ=MN/f0,脈寬調制信號fPWM的占空比DPWM與fs成正比。

![]()

評論