基于FPGA的數字量變換器測試系統設計

2.4 勤務信號發送模塊實現

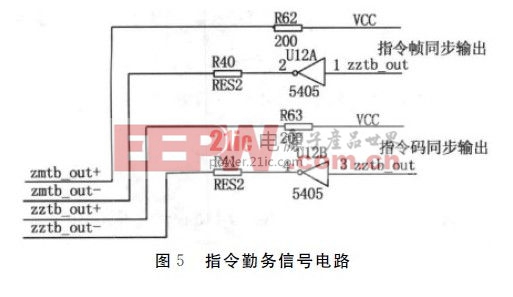

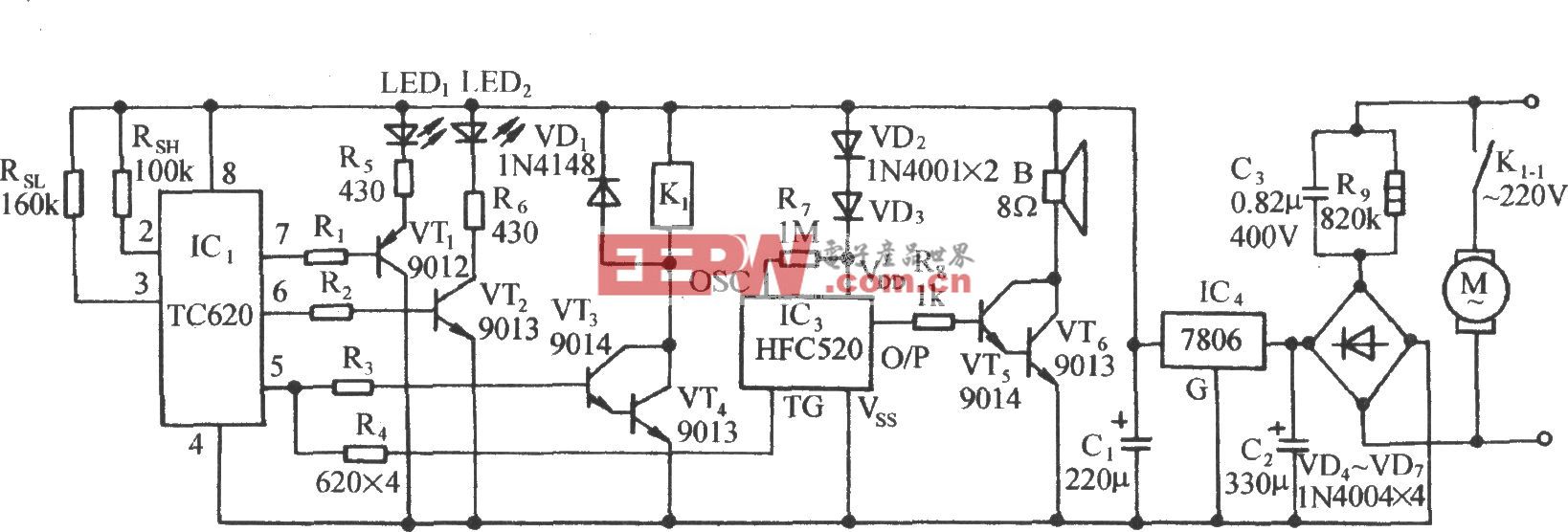

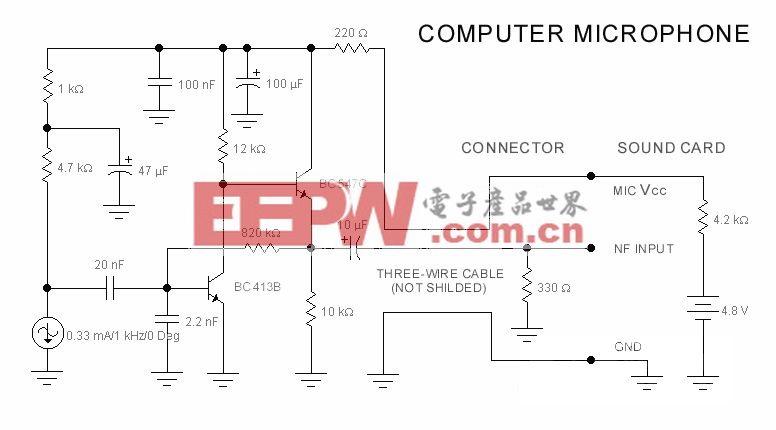

計算機字信號和指令信號都有相應的勤務信號來滿足時序要求,一般勤務信號就是指幀、碼同步信號,對其他信號的產生和接收起到時序基準同步的作用。指令勤務信號的電路原理如圖5所示。計算機字勤務信號與其原理相同。根據系統的信號輸出要求,即幀、碼同步信號的幅值和電流驅動能力的要求,采用非門芯片SN5405J作為驅動電路來滿足設計要求。

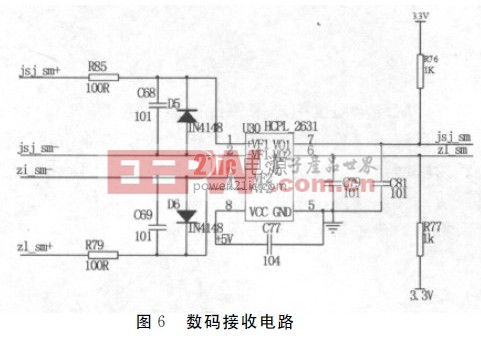

2.5 數碼接收模塊實現測試系統需要接收經變換器處理之后的信號,變換器以數碼方式回傳給測試系統,包括計算機數碼和指令數碼,兩者的接收原理相同。設計采用光耦隔離的方式對數碼信號進行接收,其電路原理圖如圖6所示。

光電耦合器采用TI公司的HCPL-2631,它具有電絕緣能力和抗干擾能力,并且能有效的抑制各種噪聲和尖峰脈沖干擾。它的兩個輸入端分別接收計算機字數碼和指令數碼,其中在光耦輸入端連接的二極管作用是用來防止信號反跳造成內部二極管燒壞。

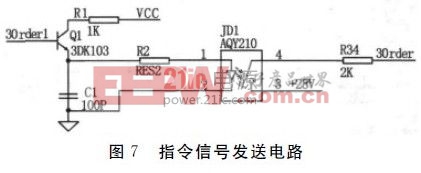

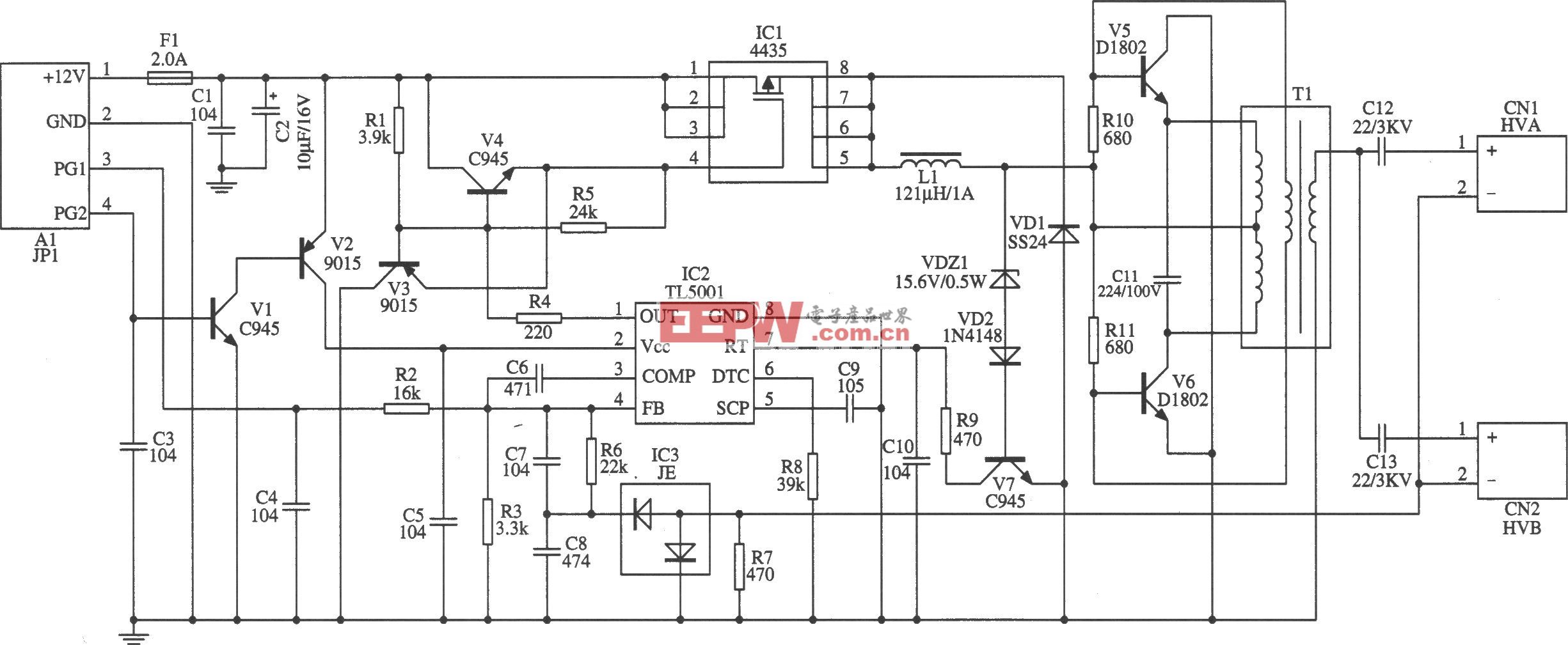

2.6 指令信號發送模塊實現

指令信號是指一種斷開或閉合的開關量信號。此模塊的128路指令信號全部采用光耦繼電器來實現,依據參數要求選擇AQY210作為控制開關的器件,它的特點是耐高壓,反應速度快,使用時間長。其單路指令信號發送電路原理如圖7所示。

由于指令信號的路數比較多,如果FPGA 的I/O口輸出直接驅動AQY210,勢必會增加FPGA的功耗。因此采用三極管對FPGA的輸出信號進行電流放大來提高控制信號的驅動能力。本設計采用NPN 型三極管3DK103,圖中3order1是FPGA的輸出信號,其為‘0’時,三極管截止;其為‘1’時,三極管處于電流放大,流經光繼電器發光管的電流13mA足以使AQY210導通。

3 系統FPGA的邏輯實現

系統主控FPGA采用的晶振是10M 和32.768M,10M的晶振經過FPGA內部分頻后來產生系統全局時鐘信號及幀同步信號,32.768M 的晶振來產生碼同步信號;從控FPGA也通過10M 晶振來提供系統時鐘。系統在上電穩定后,FPGA就會產生并發送幀同步信號(周期為25ms,脈寬為25μs),在25μs脈沖信號之后發送幀同步信號,信號的產生都是通過內部的計數器來實現的;且計算機字碼同步信號8個脈沖信號為一組、共4組,指令碼同步信號共16組。在時序上,計算機字信號的第1組碼同步信號和指令信號的第16組碼同步信號對齊。變換器在幀同步信號的上升沿的觸發下,會向測試系統發送請求脈沖。當系統收到請求脈沖信號后,通過控制FPGA延時20ms,產生移位脈沖信號和計算機字信號共同發送給變換器。在時序上,移位脈沖信號的下降沿和計算機字每位的正中間對齊。通過對從控FPGA 的邏輯控制實現指令信號的發送。FPGA對上位機的命令信號解碼后,將指令控制信號寄存在內部寄存器中,主控FPGA 通過串行通信的方式將寄存器中的命令發送給從控FPGA.發送時一組數據為10位,包括1個起始位、8個有效數據位和1個停止位,FPGA對串行數據解串,并重新編幀后將指令信號輸出至FPGA 相應的I/O.數碼的接收,都是先將數碼信號編幀后存入FPGA的內部寄存器,再通過USB將數據上傳至上位機。

4 系統測試結果

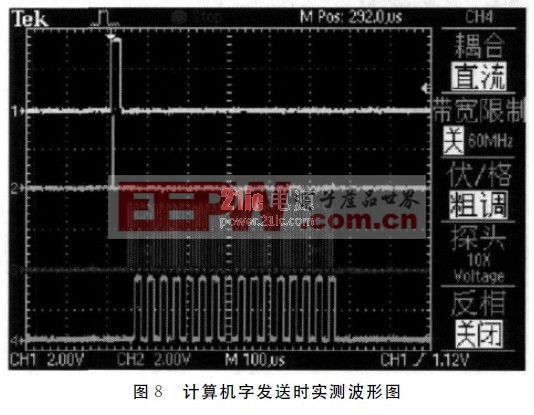

通過對系統的反復測試,來保證系統設計的可靠性。圖8為上位機發送計算機字全為AAH時測到的波形,通道1是幀同步信號,通道2是數字量變換器發送來的計算機字請求信號,通道3是移位脈沖信號,通道4是系統發送的計算機字信號。

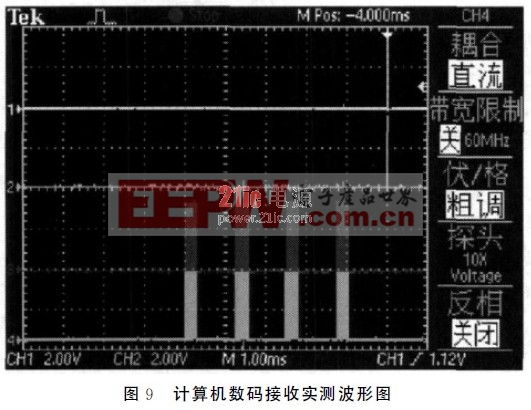

圖9是系統接收計算機數碼測的波形,通道1是幀同步信號,通道2是計算機字請求信號,通道3是碼同步信號,通道4是計算機字數碼信號。

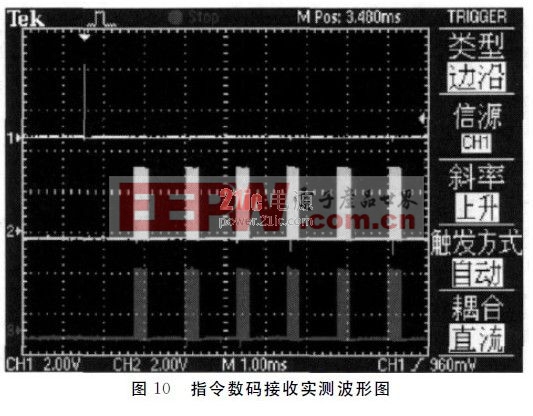

因為指令信號是以并行方式發送的,所以不涉及到時序波形的問題。圖10是指令信號都發送55H 時,接收指令數碼測得的波形。圖中通道1是幀同步信號,通道2是碼同步信號,通道3是指令數碼信號。可以看出信號的效果滿足設計要求而且精度較高。

5 結束語

該測試系統充分利用FPGA強大的內部邏輯功能和與外圍硬件電路的設計,來達到系統的測試功能。通過測試系統和數字量變換器的聯試,驗證了系統各項的輸出,對數字量變換器的性能做出權衡性的檢測。

評論