級聯PLL超低噪聲精密時鐘抖動濾除技術研究

本文針對全方位的信號路徑系統中的高速全差分運放及高頻寬14位模擬/數字轉換器的隨機及固定時鐘抖動,具體分析、研究了超低噪聲兼時鐘抖動濾除技術。研究選用雙級聯PLLatinum架構,配置高性能壓控振蕩器(VCXO),很好地實現了降噪和時鐘抖動濾除的作用。

本文引用地址:http://www.j9360.com/article/174665.htm0 引言

隨著電子信息技術的發展,數據傳輸在軍事航空、無線網絡基礎構建、測試與測量中發揮了巨大的作用。而時鐘作為通信終端、發射與接收定量和同步標準,成為不可或缺的關鍵部分。信號傳輸過程中,晶振參考時鐘本身具有較低的抖動,但由于IC、開關電源噪聲、數據或時鐘線的干擾引起的隨機抖動和周期抖動(PJ)對時鐘質量及系統性能都有比較大的影響。

典型的信號路徑設計由信號傳感器、模擬信號處理區塊、數據轉換器、接口及數字處理區塊等多個不同環節組成,為了使系統充分發揮性能,路徑所采用的主要元件必須符合有關要求。以模擬/數字轉換器為例,系統設計工程師希望其信噪比(SNR)須不可低于60dB,因此14位的高頻寬、頻率要求高達1Gpsp的數據轉換器被得以使用。在系統設計和使用的過程中,使用數據信號和參考時鐘定位采樣是重要環節,高精密時鐘發生技術進而成為亟待發展的技術之一。通常情況下,設計所使用的單鎖相環(PLL)式時鐘發生器在工作過程中,乘法器會放大時鐘抖動,同時引入其自身抖動,無法滿足均值抖動指標Jrms1ps@(12KHz~20MHz)的要求。

為了實現超低噪聲精密時鐘的發生,筆者對級聯式PLL時鐘抖動濾除技術做了研究和探討,并對系統時鐘抖動做和具體分析。

1.雙級聯PLL降噪濾抖設計

當輸入噪聲較大時,系統具有較窄的環路帶寬如幾十Hz到幾百Hz的情況下,借助本地高性能的壓控振蕩器,如VCXO、OCXO等,可以把參考時鐘輸入的噪聲濾除干凈,鎖相環輸出優越于參考時鐘抖動性能的時鐘信號。

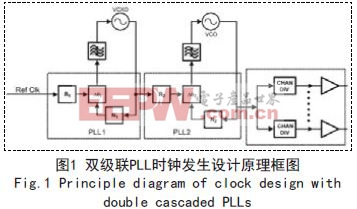

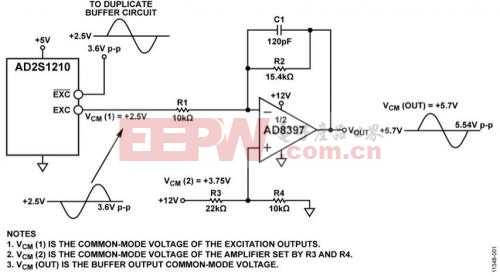

如圖1所示,時鐘發生采用了級聯的雙重PLL架構,以清除信號抖動,圖中在VCO輸出之后,續接了一個時鐘分配電路。

第一個PLL采用了很窄的環路帶寬,以便讓外接的VCXO的頻率鎖定到輸入的參考時鐘信號上。極窄的環路帶寬可以抑制參考時鐘信號中的大部分相位噪聲,使得VCXO的相位噪聲成為主要的噪聲分量。頻率被鎖定后的VCXO作為基準時鐘輸入第二個PLL,后者采用了較大的環路帶寬,以便實現內置的VCO的鎖定。這一較大的環路帶寬意味著VCO的相位和頻率都鎖定到VCXO上,因此VCXO的噪聲成為主要分量。

對于高于環路帶寬的信號相位噪聲,內部的VCO的相位噪聲和輸出分頻器與驅動器將決定輸出信號的相位噪聲。

式(1)表明,總的噪聲是基準時鐘噪聲、PLL噪聲和VCO噪聲的加權和:

加權函數H(f)是低通閉環傳遞函數,其中包含了電荷泵增益、環路濾波器響應、VCO增益和反饋通路(N)計數器等參數。該式表示了圖1所示的每一級PLL的輸出端的噪聲模型。基準時鐘信號噪聲的增益(GREF)以及PLL噪聲的增益(GPLL)也是具體的環路參數的函數。這里我們并不對這些增益和閉環響應H(f)的表達式進行推導,作為結論討論。一般來說,構成H(f)的合成器件的諸多參數以及在式中所給出的增益值都可以由設計者來調整,其選擇的標準是讓合成器的輸出端的總噪聲(STOTAL(f))最小化。在這種情況下,最小化意味著合成后的總噪聲的最小化。當對PLL2使用該噪聲方程時,SREF(f)代表VCXO的噪聲。SPLL(f)和SVCO(f)是由器件的特性所決定的,但SREF(f)取決于設計者所選用的VCXO.

2.技術分析與仿真

2.1 相噪分析

筆者的實驗及仿真參數選取如下,PLL1:

125MHz的普通晶體參考輸入,R=120,N=120,100uA的電荷汞電流;PLL2:NBXHGA019 125MHz的參考晶振輸入,R=2,N=10,內部VCO分頻設置為2,環路帶寬以366kHz,相位余量為85.5度的4階環路濾波,3.2mA的電荷汞電流;輸出方式為LVPECL,同步輸出分頻選擇各有不同,在2~510之間做隨機選擇。

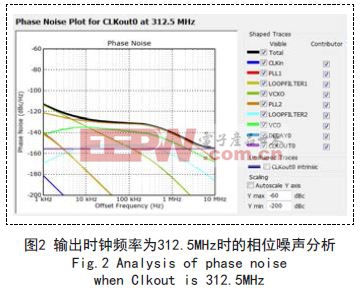

圖2是輸出時鐘頻率為312.5MHz的相位噪聲分析。相噪由參考輸入的V C X O噪聲、PLL開閉環噪聲、內部VCO噪聲共同決定。圖中表明,總的相噪在1.000kHz處的相位偏移為-113.09dB/Hz,100.000kHz處-128.46dB/Hz,10,000.000kHz處-155.22dB/Hz.

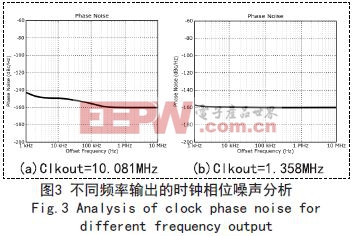

如圖3所示為輸出時鐘頻率分別為10.081MHz和1.358MHz時的時鐘相位噪聲分析圖,由三者比較可知,隨著輸出頻率的增加,相位噪聲逐漸減小,使傳輸過程中的信噪比降低至系統所需60dB以下,滿足設計需要。

2.2 RMS抖動特性

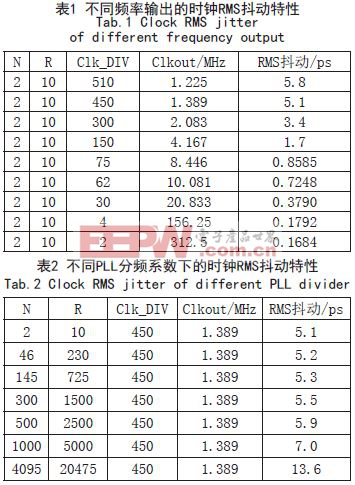

均值(RMS)抖動是表征時鐘抖動的重要參數。如表1所示,為筆者在采樣點數為1001,最低1kHz和最高10MHz的抖動探測中獲取的不同頻率輸出下的RMS抖動情況。在PLL分頻系數不變的情況下,測量得到的RMS抖動隨著頻率的增加逐漸減小,當頻率為312.5MHz時,抖動為168.4fs,而用與提供基準的參考時鐘的0.5pf相比有了極大的提高與改進。表2為不同分頻系數下輸出時鐘RMS抖動情況,可以很明顯得看到抖動隨系數的增加在呈現指數的增長。

3.結論

由仿真和研究可知,雙級聯PLL架構時鐘發生設計,在實現抖動濾除低于300fs的同時,亦可實現多路頻率合成及極低相位噪聲(RMS抖動低至1.8ps@10KHz~5MHz)。超低抖動、低功耗的時鐘發生技術滿足了信號路徑設計的模數轉換采樣及時鐘和信號保證條件,同時,此類設計也可以被應用于無線基站、微波通信和100GE數據通信領域等。

評論