基于C8051F121視頻疊加系統的設計

0 引言

目前,各種數字視頻監控系統在高速公路、電力、銀行等領域得到了廣泛應用。實時圖像跟蹤系統的應用也日益廣泛與深入,對它的終端視頻監視系統能實時、直觀地反映目標跟蹤情況提出更高的要求,因此它的顯示作用也變得尤為重要。數字視頻監控系統常常采用在屏顯示OSD(On Screen Display)技術來實現人機界面的交互。實際上,在屏顯示技術就是在視頻圖像上疊加文字,從而使顯示屏幕能夠為用戶提供更多的附加信息。

隨著數字技術和單片機技術的高速發展,大規模可編程邏輯器件的普及,可設計用一片高性能單片機,利用現場可編程器件FPGA對采集的視頻數字圖像做預處理,完成時序控制邏輯,實現視頻、圖形、字符疊加,經融合后的視頻信號實時送給監視系統進行顯示。

1 系統硬件結構設計

實現系統功能的基本思路是:以單片機C8051F121作為主控制芯片,結合現場可編程門陣列FPGA、高速數字信號處理器DSP和其他輔助電路,構成視頻圖像與跟蹤處理系統。

1.1 硬件系統結構圖

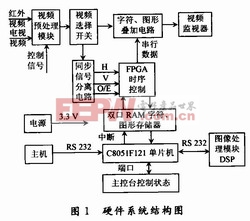

硬件系統組成原理框圖如圖1所示,其主要功能模塊有視頻信號預處理模塊、高速模數變換模塊、FPGA數字處理模塊、數字圖像存儲器模塊、DSP數據分析處理模塊、數據通信接口模塊、同步和疊加顯示模塊。

它的工作過程是:由攝像機輸出的視頻信號經嵌位、放大、濾波等預處理電路,再通過高速模/數轉換器轉換為8位數字信號輸出。同時同步機對輸入的視頻信號進行行、場同步分離,驅動地址發生器產生數字圖像數據的存儲地址,數字圖像數據在跟蹤窗口的范圍內依照地址產生器的地址按照順序存入圖像采集存儲器。

系統的時序控制采用美國Xilinx公司的FPGA實現。閃存FLASH用作存放開機自舉的程序機器碼以及有關參數數據。SDRAM是容量為512K× 32 b×4 bank的同步動態存儲器,該存儲器可用作存儲以DMA方式從雙端口存儲器RAM傳輸過來的數字圖像數據。數字信號處理器DSP執行芯片內的程序存儲區的程序,對數字圖像數據進行處理,與主機進行數據通信等工作。由高速數字信號處理器DSP和數字圖像存儲器組成的圖像數據分析處理單元對目標信號做各種圖像數據分析處理,串口部分的作用是實現與主機的數據中轉傳輸。處理窗口電路的作用是根據處理窗口數據形成顯示窗口和采集窗口。顯示窗口送至視頻復合電路供顯示和指示跟蹤效果用;采集窗口為場采集窗口和行采集窗口,可用作選通或形成圖像數據的存儲地址。視頻混合電路的作用是將顯示窗口、十字線、字符和圖像信號疊加起來,供監視器顯示。

1.2 主要部分功能

1.2.1視頻預處理

視頻預處理電路采用Maxim公司的一分四的視頻分配功率放大器MAX4138進行視頻信號的放大,以得到更清晰的信號來進行視頻處理和顯示。

1.2.2 視頻選擇開關

本系統中的多路選擇器件選用Maxim公司的4通道高速視頻多路復用器MAX441,它能根據不同的工作場合來選擇是紅外視頻還是電視視頻輸入。

1.2.3 同步分離模塊

本系統采用一款由National Semiconductor公司生產的專用視頻同步分離器LM1881,該器件能接收PAL制、NTSC制和SECAM制的全電視信號。輸出復合同步信號、垂直同步信號、奇偶場信號和色同步脈沖信號。

本設計視頻輸入是PAL制的全電視信號,LM1881從標準的負同步PAL視頻信號中分離出有效的行/場同步信號等,并將其送入FPGA以產生系統的各級邏輯控制時序。

1.2.4 FPGA邏輯控制模塊

由于系統中各個芯片的功能相對獨立,要協調這些芯片的運作,就需要一片起控制邏輯作用的可編程芯片,為此,選用了Xilinx公司的SPARTAN-Ⅱ系列的XC2S50TQ144芯片,它不僅能滿足系統的控制要求,而且也可以為將來系統的功能擴展提供控制邏輯。

評論