時鐘分配芯片在調整并行數據采集中的作用

1 經典采樣理論

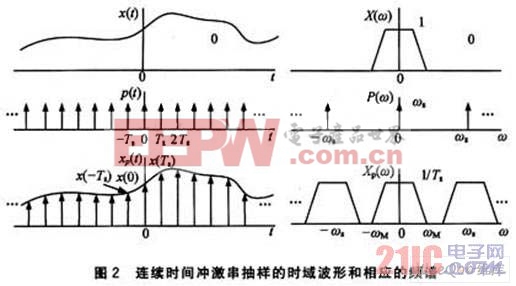

本文引用地址:http://www.j9360.com/article/170761.htm模擬世界與數字世界相互轉換的理論基礎是抽樣定理。抽樣定理告訴我們,如果是帶限的連續信號,且樣本取得足夠密(采樣率ωs≥2ωM),那么該信號就能唯一地由其樣本值來表征,且能從這些樣本值完全恢復出原信號。連續時間沖激串抽樣如圖1所示,其時域波形和相應的頻譜如圖2所示。

根據采樣定理,如果樣本點取得不足(ωs2ωM,即欠采樣),信號的頻譜將發生混疊,如圖3所示。所以如果要完整地恢復信號,必須保證足夠的采樣點。

2 多片ADC采樣方式

單片ADC采樣是最常見的。調理過的信號通過單片ADC芯片轉換成數字信號,供給后續電路進行數字處理。這種采樣方式對于一般應用的場合是可以滿足要求的,而且器件連接簡單,成本低。而在高速采樣的場合,只有提高單片ADC芯片的采樣率才能滿足要求。然而,通常高速ADC芯片都是很昂貴的;而且由于設計制造工藝,以及存儲器讀寫速度的限制,不可能無限制地提高單片ADC的采樣率。這就嚴重限制了單片ADC在高速采樣系統中的應用。本文采用多片ADC并行采樣的方式來提高系統的實時采樣率。

多片ADC芯片并行采樣的方式可以彌補單片ADC芯片采樣率低的不足。通過對ADC芯片時鐘的精確控制,可使采樣系統在單位時間內獲得更多的樣本信息。理論上,如果單片ADC芯片的采樣速率是f,那么通過M片ADC芯片的并行采樣,可以實現M·f的采樣率。多片ADC并行采樣的結構框圖如圖4所示。

評論