D類音頻系統中斬波運放電路的設計

1 引言

本文引用地址:http://www.j9360.com/article/166696.htm本文在0.35微米N阱工藝的基礎上,設計了單電源供電的全差分斬波運放電路,同時,為了減小殘余電壓的失調, 采用了T/H(跟蹤-保持)解調技術,該電路在斬波頻率150KHz工作時,輸入等效噪聲達到31.12nV/Hz。

在D類音頻放大器的運放電路設計中,信號的低諧波失真(Total Harmonic distortion)和噪聲對運放的設計形成挑戰。對于20~20KHz范圍的音頻信號而言,運放的失真主要是由電壓失調和低頻1/f噪聲引起的。而CMOS工藝相對較高的1/f噪聲和電壓失調,使得這一問題尤為嚴重。當要求電路的失調電壓低于1mV且輸入等效噪聲低于100nV/Hz時。普通的CMOS運放很難滿足需求。而常見的靜態失調消零技術,如trimming修調,雖然能很好地消除電壓失調的影響,但是卻不能降低1/f噪聲。解決這個問題的最好方法就是采用動態消零技術(dynamic offset―cancellation techniques),如自動穩零和斬波技術。自動穩零技術(Auto zero tiechnique)是通過對低頻噪聲和失調進行采樣,然后在運算放大器的輸入或輸出端將它們從信號的瞬間值中減去,實現對失調和噪聲的降低。由于自動穩零技術使用的是電容采樣的原理,因此在電路工作中極易將寬帶熱噪聲折疊到基帶頻率內,并且運放的帶寬越寬,采樣電容上的噪聲也越多,通常高達70nV/Hz。斬波技術(Chopper Technique)是采用調制和解調原理,將低頻噪聲和失調搬移到高頻部分,使用低通濾波濾除,由于沒有熱噪聲的混疊,因此運放的噪聲電壓比自動穩零技術的更低。但是斬波開關電荷注入和電荷饋通效應的影響,仍然可以產生100uV左右的殘余電壓失調(residual offset)。而且斬波開關的使用,器件的熱噪聲電平將會有所增加。

2 斬波運放的工作原理

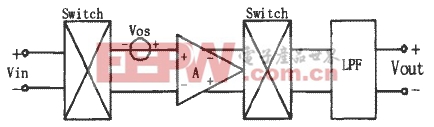

斬波運放的原理如圖1所示,其中Vin是輸入音頻信號,被頻率為fch,幅度為1的斬波開關調制,根據奈奎斯特采樣原理,為了避免信輸入信號的混疊,fch必須遠大于2倍的信號帶寬。

圖1 斬波運放的原理

經過調制后,信號的被搬移到斬波方波的奇次諧波頻率上。此信號被增益為Av的運算放大器放大,同時運放的輸入噪聲和輸入失調電壓也被運放放大,運放的輸出經過幅度為1,頻率為fch的斬波開關調制后,輸出信號為:![]()

從式(1)可以看出,經過第2次斬波后,輸入音頻信號被解調到低頻段,而運放的電壓失調和低頻噪聲只經過一次調制后被搬移到斬波方波的高頻奇次諧波上,通過低通濾波后,輸出信號中的高頻分量被濾除,低頻分量還原為音頻信號,從而實現了對音頻信號的精確放大。

對輸出信號進行傅立葉分析,得到運放的最終輸入噪聲譜密度(PSD)為:![]()

其中系數K與工藝的噪聲參數有關。

3 運放電路的設計

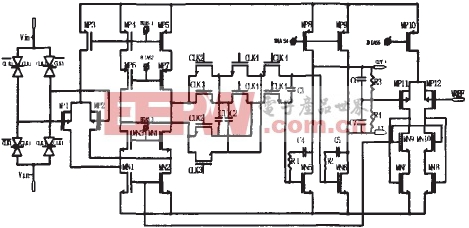

本文設計的斬渡放大器為CMOS全差分電路結構。由斬波開關、主運放電路、輸出級和共模反饋電路四部分組成。電路的工作電壓范圍2.5V~5.5V。斬波運算放大器的電路結構如圖2所示。

圖2 斬波運放的電路結構

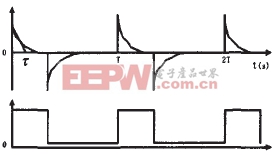

輸入斬波開關完成對音頻信號的調制作用,斬波開關在時鐘上沿和下沿都會引入殘余電壓失調,圖3為零輸入時殘余失調電壓的波形。

圖3(a)殘余失調電壓(b)斬波信號

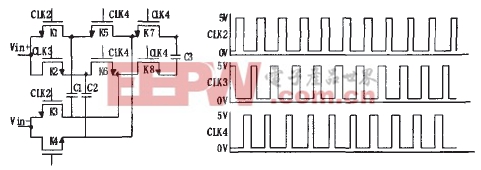

圖4T/H解調及控制時序

通過對CMOS開關特性分析可以得出等效輸入殘余失調電壓為Vos,rmts=2Vspiketfch,其中t是MOS開關的時間常數,從此式可以看出消除殘余電壓失調有三種方法:

1.降低斬波頻率:

DIY機械鍵盤相關社區:機械鍵盤DIY

評論