基于PCIe總線的航空視頻采集記錄系統的設計

摘要:PCIe總線不僅硬件接口簡單,軟件和PCI總線完全兼容,而且傳輸速度數十倍于PCI總線。針對載機任務系統實時視頻采集記錄的需求,設計了一種基于PCIe總線的航空視頻采集記錄系統,利用現場可編程邏輯器件(FPGA)實現了視頻數據流的編解碼和PCIe橋接口的設計,簡化了硬件接口設計,提高了系統的工作效率。系統在某型數字化對抗訓練系統中的實際應用表明該設計實用可行。

關鍵詞:PCIe總線;視頻采集;硬件設計語言;INDS

0 引言

航空電子系統之間以傳遞狀態數據和控制數據為主,因為數據量不十分巨大,對傳輸速率要求并不高。例如,最流行的航空總線ARINC 429和1553B總線,速率分別是100kbps和1Mbps。而隨著飛行訓練強度和精度的提高,飛行試驗和訓練過程的多通道視頻畫面需要實時記錄下來以便進行事后分析評估和系統設計改進。與傳輸狀態控制信息相比,這些視頻數據是巨量的,對航電系統的海量存儲和數據高速傳輸都提出了更高的要求。本文提出一種航空視頻采集記錄系統的設計方案,采用速率高達2.5Gbps的PCIe總線構建系統,PCIe總線既有高速的數據傳輸能力,又有良好的外設接口,有利于大容量信號的實時傳輸。有效解決了機載多通道視頻數據的實時采集與記錄,為航空訓練任務系統的事后評估和性能分析改進提供了便捷的手段。

1 系統的方案設計

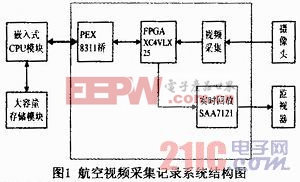

在航空視頻采集記錄系統中,攝像頭把載機任務系統的實時畫面視頻數據按預定格式組幀,通過LVDS信號總線傳輸給視頻采集模塊;經過視頻采集模塊對LVDS信號電平進行變換處理后,將單端視頻數字信號送給可編程邏輯器件(FPGA)進行視頻解碼處理。解碼后的數字視頻,一方面通過SAA7121視頻編碼器直接送給監視器,讓飛行員實時掌握訓練情況與效果:另一方面通過高速PCIe總線傳送給嵌入式CPU模塊進行視頻數據壓縮存儲,供事后分析。航空視頻采集記錄系統總體結構如圖1所示。

2 系統的硬件設計

系統的硬件設計主要集中在各個功能模塊的電路設計上,是軟件設計和系統調試的平臺基礎。硬件設計應該保證系統運行的高可靠性,在滿足要求的前提下,盡量減少可編程邏輯、系統軟件的設計與調試的難度。

2.1 視頻數據采集

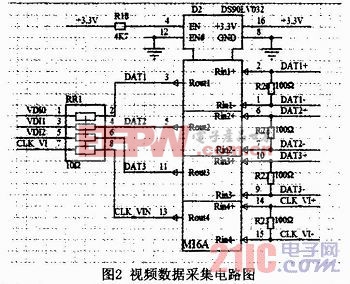

攝像頭攝錄的視頻數據以LVDS差分電平信號進行傳輸,需要進行電平信號轉換才能進行后續視頻信號的記錄處理。攝像頭傳輸的視頻數據包括4對LVDS差分信號,CLK+/CLK-是采集數據的時鐘,其余3對差分信號包含著像素灰度。差分信號經過DS90LV032轉換,變成4個單端的數字信號,供后面的電路處理。視頻采集電路如圖2所示。

因為視頻數據頻率較高,經過轉換后的單端信號應該端接10 Ω的電阻以抑制反射,提高信號穩定性。

2.2 視頻解碼和處理

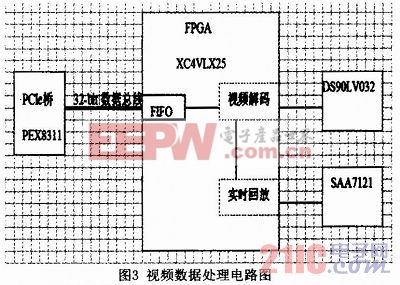

對前端采集的視頻數據,必須進行處理才能實時顯示和壓縮存儲。由于視頻數據量大,為達到最流暢的快速處理,應該由硬件邏輯直接進行數據處理。視頻數據的解碼和處理主要由FPGA完成,也是可編程邏輯設計的主要任務。

當前端DS90LV032將經過信號轉換以后的視頻數據傳輸給FPGA,由FPGA完成視頻信號的解碼還原、格式轉換后同步傳輸給CPU模塊進行實時記錄和實時回放視頻模塊。FPGA視頻數據處理的硬件接口設計如圖3所示。

評論